The following concept I have explained a simple yet viable solar grid tie inverter circuit which can be modified appropriately for generating wattage from 100 to 1000 VA and above.

What's a grid tie inverter

It's an inverter system designed to work just like an ordinary inverter using a DC input power with an exception that the output is fed back to the utility grid.

This added power to the grid may be intended for contributing to the ever increasing power demands and also for generating a passive income from the utility company in accordance with their terms (applicable in limited countries only).

For implementing the above process, it's ensured that the output from the inverter is perfectly synchronized with grid power in terms of RMS, waveform, frequency and polarity, for preventing unnatural behavior and issues.

The proposed concept designed by me, is yet another grid tie inverter circuit (not verified) which is even simpler and reasonable than the previous design.

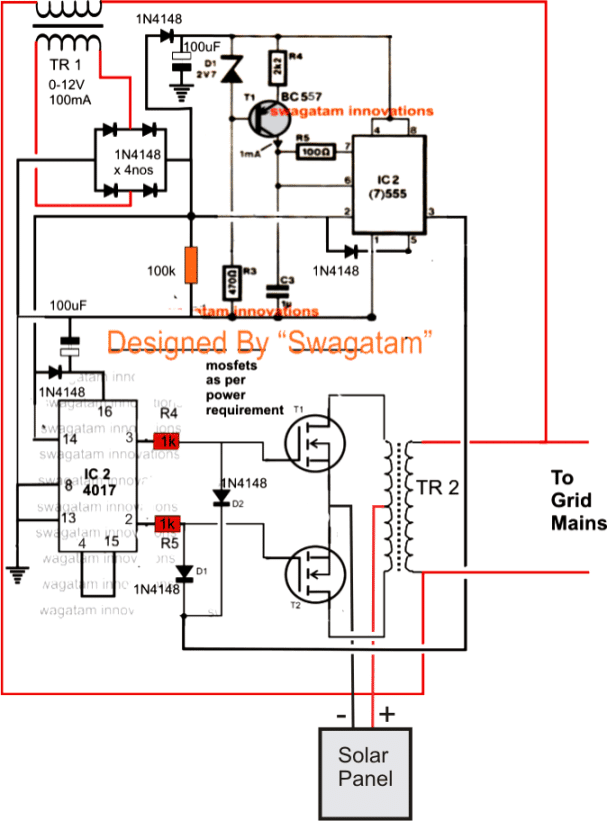

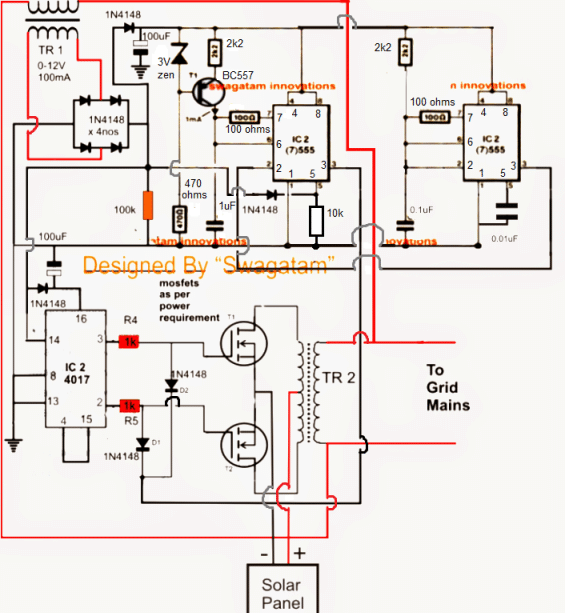

The circuit may be understood with the help of the following points:

How the GTI Circuit Works

AC mains from the grid system is applied to TR1 which is a stepped down transformer.

TR1 drops the mains input to 12V and rectifies it with the help of the bridge network formed by the four 1N4148 diodes.

The rectified voltage is used for powering the ICs via the individual 1N4148 diodes connected across the relevant pinouts of the ICs, while the associated 100uF capacitors make sure that the voltage is appropriately filtered.

The rectified voltage acquired just after the bridge is also used as the processing inputs for the two ICs.

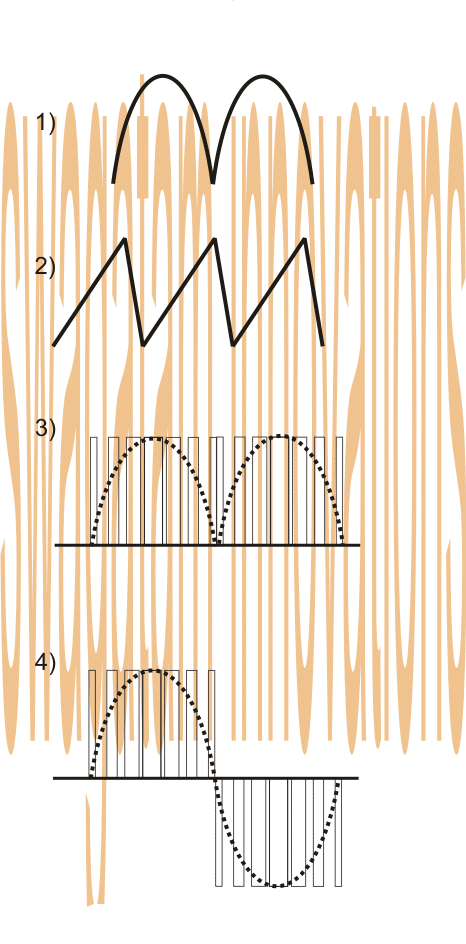

Since the above signal (see the waveform image #1) is unfiltered it consists of a frequency of 100Hz and becomes the sample signal for processing and enabling the required synchronization.

First it's fed to pin#2 of IC555 where it's frequency is used for comparing with the sawtooth waves (see waveform #2) across pin#6/7 obtained from the collector of the transistor BC557.

The above comparison enables the IC to create the intended PWM output in sync with the frequency of the grid mains.

The signal from the bridge is also fed to pin#5 which fixes the RMS value of the output PWM precisely matching with the grid waveform (see waveform #3).

However at this point the output from the 555 is a low in power and needs to be boosted and also processed such that it replicates and generates both the halves of the AC signal.

For executing the above, the 4017 and the mosfet stage is incorporated.

The 100Hz/120Hz from the bridge is also received by the 4017 at its pin#14 which means now it's output would sequence and repeat from pin#3 back to pin#3 such that the mosfets are switched in tandem and exactly at the frequency of 50Hz, meaning each mosfet would conduct 50 times per second, alternately.

The mosfets respond to the above actions from the IC4017 and generate the corresponding push pull effect over the connected transformer which in turn produces the required AC mains voltage at its secondary winding.

This may be implemented by supplying a DC input to the mosftes from a renewable source or a battery.

However the above voltage would be an ordinary square wave, not corresponding to the grid waveform, until and unless we include the network comprising the two 1N4148 diodes connected across the gates of the mosfets and pin#3 of IC555.

The above network chops the square waves at the gates of the mosftes accurately with respect to the PWM pattern or in other words it carves the square waves exactly matching the grid AC waveform, albeit in PWM form (see waveform #4).

The above output now is fed back to the grid conforming the grid specs and patterns accurately.

The power output can be altered right from 100 watts to 1000 watts or even more by appropriately dimensioning the input DC, the mosfets and the transformer ratings.

The discussed solar grid tie inverter circuit remains operative only so long as the grid power is present, the moment utility mains fails, TR1 switches OFF the input signals and the entire circuit comes to a halt, a situation that's strictly imperative for grid-tie inverter circuit systems.

Warning: The author cannot be held responsible for the results of the experiment. Please do it at your own risk!! The projects explained here are recommended only for the experts in the field of electronics.

Circuit Diagram

Assumed Waveform Images

Something's not right in the above design

According to Mr. Selim Yavuz the above design had a few things which looked doubtful and needed correction, let's hear what he had to say:

Hi Swag,

hope you're well.

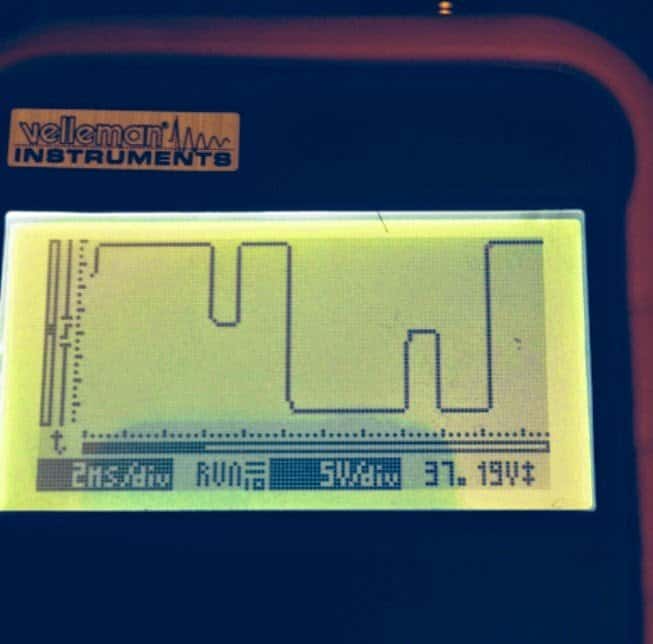

I tried your circuit on a bread board. It seems to work except pwm part. For some reason, I get a double hump but no real pwm. Could you please help me understand how 555 does pwm? I noticed that 2.2k and 1u create a ramp of 10ms. I believe the ramp should be much faster than that as the half wave is 10ms. May be I missed a few things.

Also, 4017 does a clean job switching happily back and forth. When you power up, the 100 hz clock makes the counter always start from 0. How can we assure that it always in phase with the grid?

Appreciate your help and ideas.

Regards,

Selim

Solving the Circuit Issue

Hi Selim,

Thanks for the update.

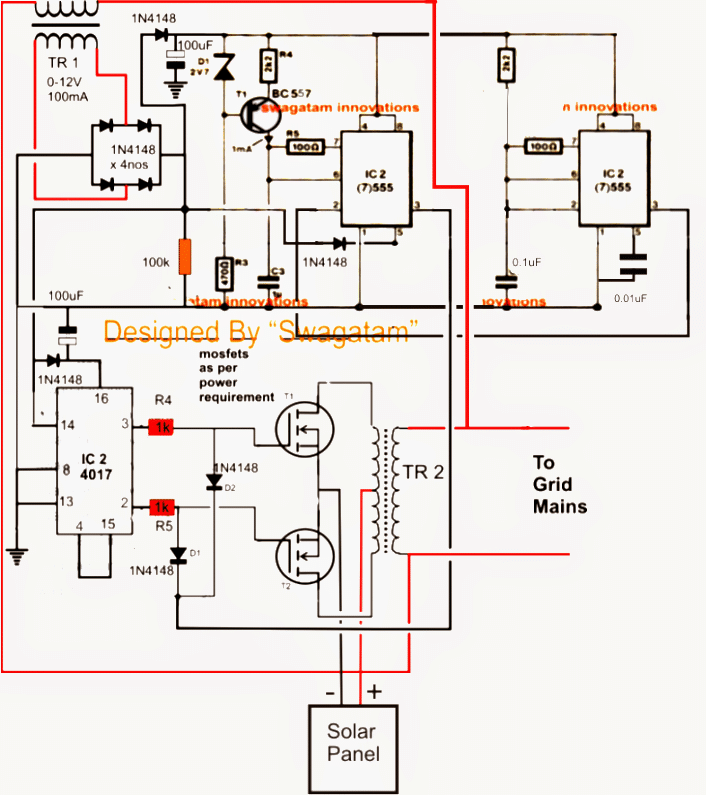

You are absolutely correct, the triangle waves should be much higher in frequency compared to the modulation input at pin#5.

For this we could go for a separate 300Hz (approximately) 555 IC astable for feeding pin2 of the pwm IC 555.

This will solve all the issues according to me.

The 4017 should be clocked via 100Hz received from bridge rectifier and its pin3, pin2 should be used for driving the gates and pin4 connected to pin15. This will ensure perfect synchronization with the mains frequency.

Regards.

Finalized Design as per the above conversation

The above diagram has been redrawn below with distinct part numbers and jumper notations

WARNING: THE IDEA IS BASED SOLELY ON IMAGINATIVE SIMULATION, VIEWER DISCRETION IS STRICTLY ADVISED.

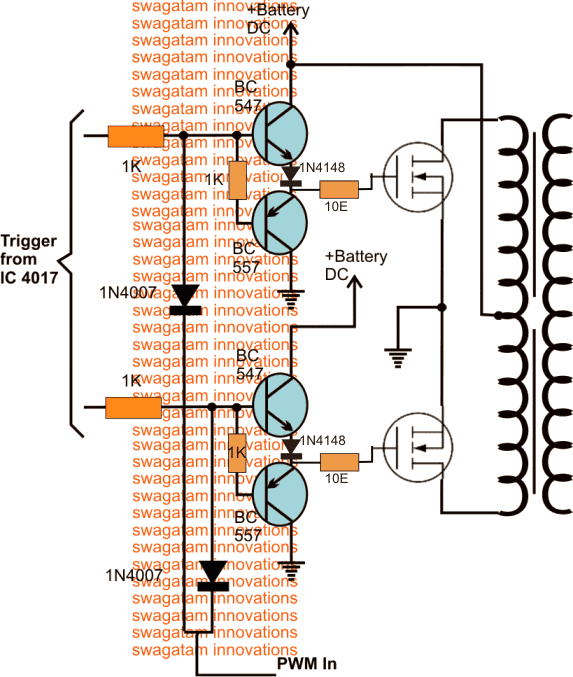

A major issue with the above design faced by many of the constructors was the heating up of one of the mosfets during the GTI operations. A possible cause and remedy as suggested by Mr. Hsen is presented below.

The proposed correction in the mosfet stage as recommended by Mr. Hsen is also enclosed here under, hopefully the said modifications will help control the issue permanently:

Hello mr. Swagatam:

I watched again your diagram and I am firmly convinced that the gates of the MOSFETs will reach a modulating signal (HF PWM) and not a simple signal 50 cs. Therefore I insist, a more powerful driver the CD4017 must be incorporated, and the series resistance should be of a much lower value.

Another thing to consider is that at the junction of the resistor and the gate should not be another added element, and in this case I see going to the diodes 555.

Because this may be the reason why one of the heats MOFETs because it can self oscillate. So I think that the mosfet heats because it is oscillating and not because of the output transformer.

Excuse me, but my concern is that your project succeed because I feel very good and it is not my intention to criticize.

Yours affectionately, hsen

Improved Mosfet Driver

As per the suggestions from Mr Hsen, the following BJT buffer could be employed for ensuring that the mosfets are able to work with better safety and control.

Ideally it is strictly recommended to calculate all the parameters before designing a proper Grid Tie inverter. Below explained are the key formulas and calculations pertaining to grid-tie inverters which includes power, voltage, and efficiency parameters:

Power Flow in Grid-Tie Inverters

Grid-tie inverters are designed to inject power into the grid while maintaining grid synchronization. The key relationship for power flow can be given as:

- Pin = Pout + Ploss

Where:

- Pin = Input power from the DC source (like a solar panel)

- Pout = Output power injected into the grid

- Ploss = Power losses in the inverter (maybe due to switching, conduction, and transformer losses)

Inverter Efficiency

The efficiency of a grid-tie inverter could be defined as:

- Efficiency (%) = (Pout / Pin) × 100

Where:

- Pout = AC power output to the grid

- Pin = DC power input from the source

You can normally assume grid-tie inverters to have have efficiencies between 90%–98%.

Power Factor (PF)

Grid-tie inverters normally needs to operate at a high power factor to ensure efficient power transfer to the grid. The power factor can be calculated as:

- PF = Pout / (Vrms × Irms)

Where:

- Pout = Real power output (W)

- Vrms = RMS grid voltage (V)

- Irms = RMS current injected into the grid (A)

Ideally for any grid-tie inverter you must try to get a PF ≈ 1 (purely resistive load).

Maximum Power Point Tracking (MPPT)

Grid-tie inverters configured with MPPT can adjust the input voltage to maximize power extraction from the source. The key equation for calculating maximum power can be calculated using the formula:

- Pmax = Vmp × Imp

Where:

- Pmax = Maximum power output of the DC source (W)

- Vmp = Voltage at maximum power point (V)

- Imp = Current at maximum power point (A)

Sizing the Inverter

Always make sure the inverter is rated to handle the peak power of the DC source. For a solar panel integration, you can use the following formula:

- Pinv = Parray / ηinverter

Where:

- Pinv = Rated power of the inverter (W)

- Parray = Total power of the solar array (W)

- ηinverter = Efficiency of the inverter (decimal)

Lets solve an Example Grid tie Problem as given below:

Consider we have an solar panel array rated at 5 kW and the inverter efficiency is 95% then the inverter should have a rating of:

Pinv = 5000 / 0.95 ≈ 5263W

RMS Voltage and Current

The RMS values of voltage and current injected into the grid can be calculated as:

- Vrms = Vpeak / √2

- Irms = Ipeak / √2

Where:

- Vpeak = Peak voltage of the AC waveform (V)

- Ipeak = Peak current of the AC waveform (A)

Synchronization with the Grid AC Line

We have to ensure that the inverter must match the grid's voltage, frequency, and phase to inject power. The key relationship is given by the formula:

- Grid Frequency = Inverter Frequency

Total Harmonic Distortion (THD)

The inverter must be designed to minimize the harmonic distortion in the current injected into the grid. This THD can be calculated as:

- THD (%) = (√(I22 + I32 + ... + In2) / I1) × 100

Where:

- I1 = Fundamental frequency current

- I2, I3, ..., In = Harmonic currents

In order to comply with the terms of the grid supply network, make sure the THD is typically less than 5%.

DC Link Capacitor Sizing

In grid-tie inverters we use the DC link capacitor to smooth the input DC voltage. Its value can be estimated as:

- Cdc = Iload / (4 × f × ΔVdc)

Where:

- Cdc = DC link capacitance (F)

- Iload = Load current (A)

- f = AC grid frequency (Hz)

- ΔVdc = Allowed ripple in DC link voltage (V)

Transformer Turns Ratio

If you are using a transformer in your grid-tie inverter for isolation then the turns ratio can be calculated as:

- N = Vgrid / Vdc

Where:

- N = Turns ratio

- Vgrid = RMS grid voltage (e.g., 230V or 120V)

- Vdc = DC input voltage

Reactive Power (Q)

Your inverters can inject reactive power in the grid so if required you can calculate it as:

- Q = Vrms × Irms × sin(θ)

Where:

- θ = Phase angle between voltage and current

Grid Current Calculation

The current injected into the grid can be calculated using Ohms law as:

- Igrid = Pout / Vrms

Example Calculations

Example 1: Efficiency Calculation

- Input power (Pin): 5000W

- Output power (Pout): 4800W

Efficiency = (Pout / Pin) × 100

= (4800 / 5000) × 100 = 96%

Example 2: RMS Current

- Pout = 4800W

- Vrms = 230V

Irms = Pout / Vrms

= 4800 / 230 ≈ 20.87A

I wonder if this scheme is functional , because I need grid tie to work 100W .

It is an experimental setup, you will need to test it on a small scale and verify whether it suits your application or not…

sello,

Got a question and a suggestion: on increasing the frequency of the 2 / 555s your using -= why not kidk them up to the 50 kHz frequency you specify in your 5kVA inverter — it will follow the grid input frequency – just chopped up more – for a better sinewave.

The suggestion is swapping out the BC547 drivers for Microchip TC4420 6 Amp drivers fro my IRF 740 MOSFETs I’ve used for years,

Hope you get back to me on the frequency question.

Hi, thanks for your interesting question and a good suggestion.

If the frequency is increased then the transformer will need to be a ferrite core based transformer, an iron core won’t work.

Sure, any good MOSFET driver as suggested by you can be used for enhancing the MOSFET switching.

The idea that I’m waiting for.

For safety reason and research purpose, I will utilize a small transformer to mimic the grid.

It will sync in a low voltage environment, about 12Vac. Even a 3 phase grid is also safe.

Best Regards

Dear Sir,

On GRID TIE INVERTER, Should I use IGBT as a final full-bridges? cause i have burned a lot of mosfet on it.

Thanks in advance

Hello Tamcat, if you build and check the stages step-wise with an oscilloscope then the mosfets will not burn. You must try with mosfets only initially, but only after understanding all the stages step wise

hello i really like to test the inverter circuit designed by you but wonder if the tr2 transformer is ferrite excluding the loops of the wire according to the above diagram, what frequency should be taken

TR2 can be a iron core transformer, so the frequency of the PWM can be set to around 200 Hz.

Sir, soon I’m going to experiment above circuits.

Pls suggest if have anybody workouts.

I’m a solar hobyest enterprising from rural India.

I have selective apx.60 projects to expt. pl contact me to know the coponent sources etc.

Hello Rajeso, I have designed these circuit with my knowledge and research, I have not yet tested it practically.

Which part of this cct ensures the phase of solar fed in is same as grid phase?

The IC2 pin5 stage. It gets the sine wave amplitude information from the bridge rectifier and chops the output waveform with equivalent PWM so that the inverter AC output is exactly equivalent to the existing grid mains AC

Hello sir. I’m Abel and I enjoy visiting your blog and exploring the projects you post. I have a problem of my own though. I’ve just bought 4 X 330 watt solar panels. I need to run a fridge directly from the solar panels without using batteries. The total series voltage I get is 140 volts. Can you please help me with a circuit to achieve this. Thank you very much sir.

Thank you Abel for liking my posts and visiting this site! Can you please provide the voltage and wattage specifications of the fridge, is 220V rated or 110V? I’ll try to provide yo with an appropriate solution , once I know these specs.

Hello Swagatam, my doubt is that the output phase of the inverter is the same as the network. And you would not have to have a transformer with voltage higher than the mains.

Anyway I think I can use the circuit outside the network using only the sinusoidal reference, to have a pure output.

I liked your project, thank you.

Thank you Carlos, I might have mentioned it due to fact that the lower RMS of the SPWM from the IC 555 might reduce the output voltage. However now I realize that this can be adjusted by having the primary voltage of the transformer exactly matching the RMS of the SPWM. The secondary side can be a 220V or 120V it does not need to be changed.

thanks for your work! I appreciate the effort and time that goes into making this website. the transformers for larger systems are quite costly, what do you think of the research paper regarding transformerless grid tie inverters? would it be viable to make a 5kw transformerless grid tie inverter using the following experimental designs?

https://umexpert.um.edu.my/file/publication/00005361_105654.pdf

It looks great! You can definitely use it to make a 5kva inverter.

Hi sir

How we create resitor and capcitor round 1khz frequency as our inverter requirement?

Good day sir..

Can you give me the link of clear and efficiant grid tie inverter for proteous simulation

Hi Rizwan, sorry I do not have any other design other than the above ones.

sir gud day..can I ask what is that D1 is it zener 2.7v? and sir do you have clearer schematic diagram of this ck5…and please if you have kindly send it to my email….thank you so much sir…I’m you avid follower….

Good day Sinoda, D1 is a 2.7V zener diode, but you can use any zener below 4.7V.

I’ll soon make the design clearer and update it for you in the article.

I appreciate your interest and I am Happy to help!

hi sir…good day and more power to you….I just want to ask if this ckt was already tested and running…becoz I want to build this also..thank you sir…

Hi Sinoda, it is not tested by me yet, but other readers have tested it successfully.

What will be the proposed cost of construction?

Anything between $100 to $500 depending on the wattage.

sir

first i tried this circuit on Proteus software then i moved toward hardware circuit. i am facing problems in making hard, sir On TR2 transformer 113V are appearing yet i didn’t connect with TR1,

i am using 12V, 5Ah battery

if AC mains turns off then no output appear on transformer , mean only with DC supply transformer gives no output,,,, sir Kindly tell me reason of this how can i resolve this

and one more problem is that the transformer 6-0-6 and IC556 i used in the circuit get heat up instantly , tell me reason of the heating of IC and transformer , how can i resolve this problem

Rida, this project is a significantly complex project and therefore it will need to be implemented stepwise or stagewise, very carefully. First you must build a normal inverter circuit using the three IC 555s, and a single IC 4017 and try to get 220V output from the transformer…once this is confirmed after that you can proceed with the grid transformer integration, and further on.

Please let me know if you face any problems…

Hi swag…

I tried your circuit of grid tie inverter I don’t understand the connection of ic 555 pin no3 which is output pin but why it is connect with a cathode side of diode….

Hi Mayur, the pin#3 produces positive and negative outputs alternately while oscillating, we only want the negative output to act on the gates of the mosfets, so that during the negative outputs the mosfets get switched OFF, here the positive outputs are not relevant, because the positives is already coming from the IC 4017 pins, we only need the negatives from the IC 555 to react on the gates for creating the chopping effect.

That is why the diodes are introduced in the reverse biased condition.

Hi SWAGATAM i am working on this GTI and i am using 25A battery can tell me what should be the rating of TR2. if you will tell it will resolve my problem

thanks in advance

Hi Mega, TR2 voltage rating should be slightly lower than the battery voltage and the current 5 times less than the battery AH

Hi Guys,

I am also trying to design Grid-Tie Inverter and reached this article by googling. I need to ask if any of you finally got a successful working inverter?

If yes can you guys please share the details of the working design?

It would help me to prevent reinveting the weel

Regards,

Faisal

Hi

Any update on this design? please do a final design and parts.

any update on this design? please post the final layout with parts and any comment if already tested?

the inverter is for solar would it work for a wind turbine

no it won't work for wind turbines

Thank you, have only recently become interested in the GTI, for me it was very interesting and timely

you are welcome!

Possible person benefit me how what kind of plug which is based

I am very interested in your article, I place a lot of problems like this. I want to learn a lot from your article.

I've seen articles that you provide. I want to ask, the battery was connected to the mosfet leg or TR? and, in the synchronizing voltage must be the same system, the inverter output will be the same whether the system? if not then there will be the potential difference and the GTI will be load system.

thanks Agung, the inverter is perfectly synchronized with the grid, I have tried to take care of this issue as far as possible.

The voltage may be tweaked at the start before the integration with the grid by adjusting the preset at pin5 of the first 555 IC.

Once this is adjusted to the level of the grid, the output could be joined with the grid and rest will be automatically monitored and adjusted by the circuit itself, hopefully.

Hi,

may i know witch circuit is working?

Thanks,

Oliver

Hello mr. Swagatam: According to my understanding the 4017 cd is not enough to drive the MOSFETs gates models

While by no current GATE, however this has a very high capacity parallel, and when working in this capacity derives high frequency excitation energy to gnd.

Therefore it should employ a driver to excite said MOSFETs, and also the series resistance should be no more than 10 or 20 ohms.

So I think that may be the reason why heat the MOSFETs

Hello Hsen, thanks you may be correct, but according to me the problem could be due to incorrect loading at the output of the trafo due to the absence of a neutral terminal.

mosfets are voltage dependent devices and can be driven by any CMOS IC output so I guess 4017 output would have no problems driving these devices.

a lower resistance at mosfet gate becomes crucial at higher frequencies, but here since we are dealing in Hz, the gate 1K resistance value wouldn't make much of a difference, but surely a lower value around 100 ohms could be tried.

Moreover only one of the mosfets gets hot and only when the inverter is connected with the grid, so I am suspecting the problem to be with the secondary section of the trfao.

Hi Swagatam majumdar

i have a idea . source dc solar depends on sun . it not connect on grid network . you can do a boost circult in dc source(solar input in boost ) . output alway is dc source fixed . so circuilt always on grid network.

thank's

Hi Khang,

you mean a DC to AC Gritie inverter using a ferrite cored trafo right?

it's exactly what we have discussed so far but by using a ferite core.

If possible I'll try to post it.

HI Swagatam Majumdar

I have one idea about the problem on grid .It makes circuit at any time also works on grid

m.youtube.com/watch?v=9z2WjbC8yaE

Hi mate i attached the much clearer video just. Skip to 1.43min..and sorry for the background voice just dont mind it..you will see the moving backward of the meter.

Thanks mate,now it's crystal clear, by the way how did you connect the watt meter? is it in series with the inverter output?

Hi mate i attached the video of my meter moving backward…its too slow as my battry is little damaged not enough voltage also…

http://www.youtube.com/watch?v=x-XuFsHW0sk&feature=youtu.be

good effort mate,thanks…but couldn't make out much from the video, the rotation was hardly visible.

Same here, my killowatt meter running backward only 1 round then stopped.

Hi rto make sure your wattmeter is in enough hieght and 90degrees angle…its wierd but kilowattmeter…using at home seem afected by earth magnetism…for me i put it atleast more than one meter and 90degreess anggles…all become wow..!!! And when for example brown out or no electricity your grid tie will not provide voltage or light from your home but when you see your wattmeter it spin double…in speed..oh mate…this gti is fun…actually..im like a kid playing on this thing…

Hi mate..no worry i will upload much clearer view..im using phone thats why..i will try to use my cam..and upload it 🙂

For the readers..take note this is dangerous..you'll get in prison if this is not allow in your place and get fine…from the electric company…what we are doing here with swag is purely..expiremental purpose only to prove the law of inductive and capacitve reaction in circuit…but were not actually building this thing…to used..

hi RTO

can you connected GTI output on a wattmeter(solar meter) and connect it for grid meter.you can saw solar meter run

Hello mr. Swagatam: I watched again your diagram and I am firmly convinced that the gates of the MOSFETs will reach a modulating signal (HF PWM) and not a simple signal 50 cs, therefore I insist, must be incorporated a more powerful driver the CD4017, and the series resistance should be of a much lower value.

Another thing to consider is that at the junction of the resistor and the gate should not be another added element, and in this case I see going to the diodes 555. Because this may be the reason why one of the heats MOFETs because it can self oscillate.

So I think that the mosfet heats because it is oscillating and not because of the output transformer.

Excuse me, but my concern is that your project succeed because I feel very good and it is not my intention to criticize.

Yours affectionately, hsen

OK, thank you very much Mr. Hsen, I'll update the information soon in the above article with the suggested corrections

HI Barbe I've been checking the conversation can you send me the finalized design of the circuit so I can try , I Only have a Multimeter so I Cant Improvise that's why I'm asking the finalized diagram and parts list .

Thank you.

.1 mate, no…this is actually a optocoupler mate…so no short circuit…is actually working…im running a while ago thats why no part number i will make goodone in computer…i! I just copy the concept from ur design and look for the work of 4017 and 555… So insted of using relay as its noisy and soon be burn better optocuopler on and off light only….you can make it more complex to make much more good square wave…but actually..is 80 to 100hz the output of that one u just need to adjust the caps defend…me i put 2uf…but sometime 5uf

But the tempting here mate is that is actually the kilowatt meter moving backward even digital…the only problem i have is that my kilowatt meter using for testing is hve some kind of lock after one round it just not moving but the main kilowatt meter is doing backward…can u please help me on this to remove that one..im trying to figure out but..i cant see anything…

optocoupler?? mate I'm confused,which circuit are you referring to?

I have no idea about wattmeters, let me research more, will update you once I get well versed.

Hi barbe, I made the second design which is two 555. What value you are using on C3?

a neutral is crucial at the output of the inverter

if both the terminals are "hot", one half cycle will short circuit with the neutral of the grid.

Hi swag, the caused of unbalanced voltage from pin 2 and 3 is one of my diode from PWM got leaked. Now, the voltage is equal.

I have another problem is when I test the voltage (using analog tester) of pin 2 and 3 of IC 4017, i see the pulses. When 1 diode from disconnect either from pin 2 or 3 the pulse is not visible.

Is that normal pulses from pin 2 and 3 are visible on analog tester?

Hi RTO,

pluses will not be visible under any condition.

You'll be able to measure only the average voltage levels at these points.

pulses won't be visible because the frequencies are very high and cannot be detected by voltmeters.

there could be something not right with your circuit.

Hi RTO, the same of what i get…if you have scope u will see to much interfernce…im not sure but need some filter some wher

s63.photobucket.com/user/barbe10/media/imagejpg1_zpsc1919185.jpg.html?filters[user]=139832643&filters[recent]=1&sort=1&o=0

I attached the gti without tr1 base on swg design,,,is working..i used igbt much better than mosfet

Barbe, you can also try using BJTs as shown in the following article.

BJTs are much easier to handle than mosfets and are much cheaper.

https://www.homemade-circuits.com/2012/02/how-to-make-mini-homemade.html

Hi sir

I recommend using IGBT inverter circuit for the best. igbt working at high voltage and high currents

if you use TR3 transformer to driver for Q1 and Q2 . I see it was dangerous because of Gate connecting directly to an AC source.

you can connect 2 diodes in the TR1 output transformer and a resistor at pin G, add 1 zener diode to ensure they are safe.

Hi sir

I was student of electronics, that is my opinion

thank's

Khang, Q1, Q2 are rated to work at 500V, so it's fine to use them in that way.

There's no portion in the circuit which is unsafe, I have taken care of everything,

you can specify the points which you feel are doubtful… I'll explain it to you with reasons..

I consider mate the suggestion of khang…igbt is much safer in inverter…!!! Base on my reserch to…he have alot of advantage…specially on inverter…!!!

Actually this design is already working just need some touch up i would suggest try khang the second design of swag with 2 555 ic…!!! That one is working…i try that one already..the issue on that one is not smooth squarewave output 323vac..and when u connect to the grid to much interference…on sine wave…the output frequency is to high as well like 1 to 10 khz….we need atleast an output of 90hz as we can adjust it….

Be caution if you want to try the third design…on the spot..i burnt my 2 mosfet with no idea wat wrong…!!i try to check for any mistake on my soldering nothing found..better try the second one and work with that.

Hi khang…i think you are correct and eliminate the tr1 then used 741 ic as a switch then single 555 for the pwm then 4017 or never mind the 742 is optional work with single 555 only that will work for changing input voltage…i seen that one in scope…i will try that one base with the design of swag… Im just busy at the moment with my solar panel… I need to install my gti…200watts i buy from online…hahah…though the design that im working at the moment is perfect already but im not yet finish with the relay incase there is some no power some engineer working outside they can probubly get hurt…so try the QC one already…but your suggestion is actually working i seen that with my friend similar with swag design…may be he actually copy it from him but that guy..dont want to share his thing…anyway swag is there..we can figure it out…

Hi Swag,

I made your circuit using pwm and the results are..

One of mosfet that connected on pin 3 is hotter than the other.

I just check the voltage from pin 2 and 3, the pin 2 voltage is 7v and the pin 3 is 4v.

My output transformer voltage is half of grid voltage.

Hi RTO,

the pins of 4017 should have same voltage outputs, because there's no reason for it to produce different voltages.

the PWM will need to be tweaked by adjusting the preset at pin5 of IC1 until the output voltage matches the grid voltage, before integrating

the transformer must be rated lower than the battery voltage for the above voltage matching

Hi Swagatam Majumdar

a good idea

I have a question . why not use TR1 to activate Q1 and Q2.

Solar power has always changed, the solar voltage from 0-17 . low voltage , circuit always connect grid or the power network not connect

Hi Khang, yes that's exactly what we have tried to do in RTO's circuit, you can check it out here:

https://www.homemade-circuits.com/2014/04/simplest-grid-tie-inverter-gti-circuit.html

Swag, I would like to try your circuit.

Can I use this mosfet?ph.mouser.com/ProductDetail/Fairchild-Semiconductor/RFP50N06/?qs=sGAEpiMZZMsX0CFs5rpLHrnMqvVNUDbo

sure RTO!

the mosfets is rated at 60V, 50amps, just perfect for the project, no issues.

I thnk rto is correct..that simple one is working i just try that one mate…its working also..the issue of that one has no protection…yet…on the one that i build im starting to put a scr protection switch and a line frequency monitor to maintain the tie

yes that's right

Hi Swag, i attached a link before a design work perfect with zero neutral aswell i only used normal caps as filter to the output.

s63.photobucket.com/user/barbe10/media/imagejpg1_zps88f2ccdb.jpg.html?filters[user]=139832643&filters[recent]=1&sort=1&o=0

Hi Barbe, that's great, by the way how did to check the results whether it's adding the required amps to the grid?

I used wattmeter mate…public will read this but..the meter is actually reversing..note that wat we are doing here with swag is only xperinment…we follow the law…thats it or if the mter is no reverse polarity its actually stop..the more you increase your watts the more it spin backward or otherwise even youre using airxon is the meter is too slow..:)

thanks mate, I am sure folks would be learning a lot from the discussions.

Hi Swag, the design is :(, busted first try burnt the mosfet instantly also the second and thrd design..i try the old is fine but unstable.

That's sad mate, but somehow I feel that the mosfets could be burning due to some unknown reason, not because of the grid integration, because with the neutral now added, things should become much safer.

mosfets are too sensitive devices and many factors need to be taken care of while configuring them.

Hi Swag,

I'm also follower on this project. I had read your conversation with barbe, seems the circuit is still not stable. I tried some circuit (GTI) using my old UPS parts and it's worked fine without using PMW circuit. Please see the schematic diagram and the actual project.

Yellow Tester is the Amp usage from input.

Black Tester is the voltage input.

and White is the Wattmeter from the output.

postimg.org/gallery/5l89n1by/

Thanks RTO,

I can't believe it. Can it be so simple?? It looks great, though.

I post these diagrams soon in the above article or may be I'll create a new article out of this.

I would require more feedbacks from you regarding the design.

Thanks:)

however I think the design strictly needs to have a "neutral" at the output without which things could get nasty.

A center tap at the secondary would solve the problem.

The only problem is the efficiency. I hooked up 200 watts solar panel on it and I only got 92 watts peak output.

I have discussed the design elaborately in a new article, please find it here:

https://www.homemade-circuits.com/2014/04/simplest-grid-tie-inverter-gti-circuit.html

Thanks Swag, I will try the SCR version.

BTW, I'm still waiting your GTI circuit using bridge mosfet output.

I'll try to update the full bridge version soon, but it could be a bit complicated,

after seeing your design I have lost interest in the other complex designs and want to see how it can be improved further.

The only one feature that may be lacking in your design is the voltage control features, there's no arrangement that would tie the grid voltage level with the inverter voltage level…presently the inverter voltage is solely dependent on the transformer rating….it needs to be tied in sync with the grid so that it adjusts automatically corresponding to the grid voltage.

Ah ok mate thanks…i made the primary bigger as well…im working with the board now…let see…i but one cheap wattmeter aswell…to verify xsactly the work…! I keep u posted what ever i found…

that's great mate, we'll wait for the updates.

Hi mate…i dont know actually if it is crucial or its fine..i actually calculate six O six but i think i mis one volt mate it become seven O seven mate do you think is fine?…

Hi mate, it doesn't matter much, we just need some decent margin so that the voltage can be tweaked and synchronized using this margin, that's why we need a trafo having voltage lower than the battery voltage which will facilitate setting of the output voltage right from 200V to 400V, ofcourse this whole margin won't be used……so may be even a 9-0-9V trafo will work, but 6-0-6 would provide a better and bigger margin for the adjustments.

Yeah mate into the grid and not in the grid….its become to hot any way…im rewinding at the moment my 12 0 12 to get 6 0 6…let see….how its going….you have any sugestion to make wattmeter..as i read…if thr grid tie is feeding without load watt meter should reverse if its working…if its not happening is not working…?

Is the one i show u before…the IGBT and four control transfo mate

OK mate thanks, if you can show me the new schematic, I can probably suggest something.

as for the 44n mosfet, you said it became hot only after integrating with the grid…it may be because previously we did not consider the "neutral" point at the inverter output which could be shorting the TR2 during the wrong cycles from the grid.

Let's hope the new mod in the last two diagrams above solves the issue.

Its another design i found in the net…im curious as its only transformer…like basic…but is actually work mate perfect frequency also not bad..just minor filtering will be good i evn connected to the gird and no issue i see it feeding…but i need atleastn18volt input on 0 12 to get 220volts…

In your desgn im goin to used 6 0 6….as i read that 0n 12 0 12 the primary actually rich 48pp..will that is the reason why may be my 44n get very hot and burnt….in 6 0 6 it will up to 24 volts only…which will keep my 44n in safe…but hence the frequency its high the reading on voltmeter will be defferent as u used the oscilloscope…

Let see mate what will happen im starting to make layout on the board..as my breadboard is already crack burn and not in shape…becAuse of those very high temp mosfet….

Hope we get it perfect this time…:)

Im goin to try the first one… And let you know…

all the best to you!

Sure mate…the potentionmeter im gonna na used 10k no prob? Or i need lower than that or higher i have 100k and 10k with me? What u think mate

yep, could be a 10k no probs.

For the 10k i will put in 50% yeah??? Or what should be the reading or any specific resistance into it mate??

mate, keep the slider position somewhere on the center and then by simultaneously measuring the output of TR2 adjust the preset until it's almost equal to the grid voltage, once this is done it should automatically correct itself according to the grid fluctuations.

Barbe, I would recommend that you first try the second last deign and confirm the results by tweaking the preset etc, after that you can proceed with the last design which is rather a risky one.

…for both the cases, synchronizing (by verifying) the grid phase/neutral with inverter phase/neutral is crucial.

i can only see a transformer with lots of wires and an oscilloscope trace image on the right………. i did not understand your question mate

Ah sorry mate…not this one…i mean this one….

s63.photobucket.com/user/barbe10/media/imagejpg1_zps5655eada.jpg.html?sort=3&o=0

Sorry for that one i didnt notice it.

Sure mate, the scope looks great to me, you can buy it and use it for all frequency related jobs…

Hi mate, i have delay in making your design..as spare parts here is out of stock so im ordering it online hopefully i can recieve the items by next week from hongkong….:)

OK mate no problem, we can wait!

Also im having issue in finding the p channel mosfet….!!! You have any suggestion

Ok then mate..i need to wait for this item they dont have currently in stock so hopefully by next week we can start cracking…!!! 🙂

Sure mate i will do that…im preparing the parts…and let see again…

I have list of mosfet …..could you pleas check if we can use this,

Irf710(400v/2amps N-ch)

Fqi2p40(-400v/-2amps P-ch)

Thanks Mate

yes mate, they look perfect to me for the purpose, you can try them out

Hi mate..im preparing d parts again once its ready im goin to have a blow this one again..thanks mate

mate I would recommend the single diode version first before going for the mosfet version.

also please see the inclusion of the preset at IC2 pin5, this could be used for fine tuning and matching the TR2 output with the grid voltage before integration

…also pin2 of IC1 is NOT connected to the anode of its pin5 diode

Hi Mate what is the value of the TR3, and the other Mosfet? Thanks Mate

mate, TR3 is 0-9V/220V, mosfets should be rated to handle 500V at 2amps

I would want an expert to verify the design before implementing.

Hi Mate, i have little confusion on my project regarding phase…polarity. I attached the link to find more easy to explain to you what i mean..coz on the diagram the dot of primary and secondary are both on top…while on my transformer what ever i do the polarity was different the primary dot is on top the secondary is at the bottom. Is it ok even like this right,.. correct me if im wrong i think as long as you find the +/- is no problem right. For long years i already forgot the banking and polarity of transformer. To be honest mate my job is different from what i really love to do and my hobby i work in fitness company…while at home im doing this hobby..:) anyway here is the link below;

s63.photobucket.com/user/barbe10/media/imagejpg1_zps3e737c8c.jpg.html?filters[user]=139832643&filters[recent]=1&sort=1&o=0

Thanks..Mate

Hi Mate, i think we have missed a crucial point in the whole issue.

In the GTI explained above, both the outputs will ofcourse show a LIVE response since the terminals are changing polarity 50 times per second, so your line-tester will show a glow on these terminals.

However in our home we don't face this issue, rather find one of the terminals to be in a non-active state which we call the neutral point.

In the above design there's no neutral and that's exactly why we are reeling with the problem and were unable to find the solution so far.

THe remedy is simple, use a center tapped winding at the secondary side of the trafo.

That's it, once we do this the problem will be solved once for all.

I'll update the diagram soon.

As for the diagram that you have shown, for AC the polarity or the dot becomes immaterial since the polarity would be changing in an up/down manner constantly.

ah ok mate..thanks for that…..

in update diagram..im waiting for it mate..hopefully we get it smooth.

Thanks Mate

Sure mate i will do that…thanks

Hi Mate,

Please check attched link for further analysis…what you think of this design…? At this moment im trying to figure out still whats going but still stable then not…the waveform is not continues sometimes is just cut off..maybe the 555 or the transformer..!!!

s63.photobucket.com/user/barbe10/media/imagejpg1_zpsba130c50.jpg.html?filters[user]=139832643&filters[recent]=1&sort=1&o=0

thanks mate, it's the same design that you showed me previously and it looks feasible.

the instructions written on the page are all correct and may be followed as given.

as for the inverter design shown in the above article, for te waveform info you can refer to the following link which includes an identical design but not a GTI

https://www.homemade-circuits.com/2013/10/modified-sine-wave-inverter-circuit.html

Thanks mate…this is AC caps right…..anyways on your design the 1k resistor can we make it like 100ohms? On 4017 Thnks

yes mate it's AC cap, 1k could be replaced with 100 ohms in the 4017 circuit, it's not a critical value

Thanks mate i will check that one still not hundred percent success…sometimes ok sometimes not..!! So also im going back to the book and read a little to understand much bout the circuit…!

Hi Mate, i need your help on this one they said its actually working GTI the issue is they remove the capacitor value..do you have any idea if you dont min to calculate this one or what is the value.

Im actually wanna try dis one while waiting for your next design…also xcited with that one..as that is a transformerless.

Thanks in advance for your help.

s63.photobucket.com/user/barbe10/media/imagejpg1_zps5d36adf4.jpg.html?filters[user]=139832643&filters[recent]=1&sort=1&o=0

mate, it's not too crucial, it's just for preventing peak transients from entering the devices.

as far as i know such networks are used across triacs also, and I have seen 0.1uF/400V being used for such applications.

so you can use 0.1uF/400V caps for these.

Hi Swag i found some diagram in the net but not sure about this…i will attached below the link for your analysis may be this could give an idea?

s63.photobucket.com/user/barbe10/media/imagejpg2_zps6d2ce45a.jpg.html?filters[user]=139832643&filters[recent]=1&sort=1&o=0

s63.photobucket.com/user/barbe10/media/imagejpg1_zps6078a863.jpg.html?filters[user]=139832643&filters[recent]=1&sort=1&o=1

By the way i will continue on this one and try to find something..maybe i juz miss something on this…let you know for any update…

Thanks mate for the help and support….

Thanks mate! The diagrams make sense doubt…but can't really confirm until checked practically, it also incorporates a trafo although it's synchronized and guarded by triacs so definitely looks a better one.

you can give it a try and let me know about the results.

the triacs in series with the trao output terminals makes lot of sense, so you should give this a try.

I think im going back to the breadboard…it much more easy to check….

Im just tired yesterday mate…i will start again today…

Quick question i will eliminate for the moment the big transfo and power up the circuit using the the small 12vdc supply i think thats is the safest wAy..and check how is going to work…mAy be i miss something…i will not give up on this..im just tired yesterday and blow up too manu component hahah…let start again with this mate…

Anyway if you have updated design let see aswell that one…electronics sometimes need a cup of coffee coz of the headache but cant give up…coz of the challenge…

Thanks mate…let you know of any progress….on this design

surely mate…I appreciate your interest….be assured I'll post the other concept soon using full bridge topology and without an output trafo.

On the main output mate….

barbe how it's only 32V, you said the inverter was working perfectly when not integrated to grid?

Its 323vac mate….

Hi Mate…i think im going to stop this…i think need more studies need no make…output is pure sinewave connected to grid..50hz…but i dont understand that after a minute my transformer and the mosfet, and 4017 got damaged…

I dont know where to troubleshoot because the frequecy sometimes is cut off and work again…i cant get a picture as all is so quick…i try to do it again but the same issue happens..i think you need to modify something from the circuit…yesterday was stable…and today i check with scope seems perfect to me,.,,but i dont get…those things happen when connected to grid…even frequecy are the same..maybe you mis something in the design…i dont know mate…!!!

Total damaged

10nos. 555

12nos.4017

4nos. Transformer

And also the diode is very hot too…

Hi mate, the output of the above design is perfectly in tune with the grid AC and is a sinewave, although it's PWM based.

I think here the culprit could be the transformer, which I thing should be completely eliminated, because different sets of winding could interpret the input differently no matter how much the 555s try to synchronize the grid data

However with no transformer the output stage will need to be a full bridge network using four mosfets.

soon I'll update a new design where the transformer will not be used

anyway, hard luck mate

hope you succeed finally sometime later.

in my life so far i have burnt thousands of bucks while learning the practical stuffs in electronics….that's a part and parcel of the whole thing:)

Hi Barbe,

by the way I thought you would first confirm the various stages using the oscilloscope and only after verifying them all you would go for a grid-tie??

that's exactly why we waited for the scope, right?

Hi Swag,… Any idea why im getting this reading i attached the link below,

s63.photobucket.com/user/barbe10/media/imagejpg1_zps6e6ab845.jpg.html

Hi Barbe, where are you getting this voltage, across which points?

Hi Swag as an update i attached a link below,

s63.photobucket.com/user/barbe10/media/imagejpg1_zps2eb32e0e.jpg.html?filters[user]=139832643&filters[recent]=1&sort=1&o=0

I change the zener diode on going to the mosfet 12v…but i did not put the zeners to all the ic…seems all the voltage stable…both mosfet are in normal temperature…diode from transfomer is normal….main transformer not hot…everything is normal…im juz waiting for the portable osciluscope that i buy from china… Jejej..hopefully by tomorrow i can get it…

Voltage on 2 555ic – 5-9vdc

Voltage on 4017 – 11-12vdc

Thanks Mate….

That's great mate, hopefully the scope will solve all issues that we are facing right now,

best wishes to you.

Hoping for that mate..once i get it all. the waveforms that i can get i will send it to you for further analysis…!!

At this time seems stable but i cant light up 10 watts light bulb but i think my battery is not in good shape for all the miss i made…

Anyway, how about my request mate the arc welding machine…i've watch in yourube the smallest welding maching im wondering maybe its some kind of voltage doubler not sure…all i know is the old transformer type…but know there are using inverter type..i just cant understand how to increase the Amps…to weld something

Thanks..mate

I am finding it difficult to find a working circuit with no obsolete parts. I'll keep trying and let you know if I find one.

By the way you can use 6nos of 12V/10amp smps units in parallel for implementing the arc welding through their combined outputs.

Thanks mate…no worry…!!!

ah ok…let you know then later I will put it back,…the zener diode…regarding the phase I think it is in correct phase..the buld did not light up..i even touch the neutral..its zero…will for being crazy sometimes.. I got electric shock on the other cable…hahah..:D

thanks mate for the info..

you seem to be a mad crazy scientist (just like me) haha…just joking mate.

Will..im just a follower mate…and a big fan of yours…!!!

Hi Swag…44N Mosfet is better than 540n…and also I spray an insulation varnish on the board and cable to prevent static…seems ok know…I found the neutral aswell..:)…I also remove the 12v zener diode on 555 and 4017…input is normal even I put 18vdc…10volts on 555 12 to 13 on 4017…let me know if should I put back the zeners… thanks barbe

Hi Barbe,

at 18v the ICs could get damaged, not sure how you are getting the results?? better make it into 12v before feeding them to the ICs.

Hi Swag, just update sometimes it just not working for no reason..still not working as it should be…anything that maybe u can suggest…!? Thanks barbe

Hi Barbe,

the idea is simple, the voltage from the inverter should be in-sync with the grid…that's the main idea behind any GTI.

you can confirm this by isolating the inverter output from the grid and checking the RMS voltages of the both whether they are synchronized or not.

If the voltages are synchronized, both the counterparts will "shakehands" and serve the purpose as intended.

According to the rule when two identical voltage sources are connected together with correct polarity, the net effect is zero and they won't interact negatively, in this situation the currents of the two counterparts would be simply added.

For example if your GTI generates an accurately synchronized 220V fed back to the grid at say 2 amps, while the mains grid current is say at 32 amps, it may be assumed that you are contributing 2 amps extra to the utility or 2 x 220 = 440 watts.

So the first thing you need to do is confirm whether both the outputs are synchronized or not using an oscilloscope.

as mentioned earlier, the polarity of the phases are crucial.

I hope you got the idea mate;)

6 0 6 not working and irf540 is not good to used..i think we need to increase the mosfet rating..i will try irf1010n and let see…!!!!

No, the IRF540 or any mosfet will work, it's not the mosfets that may be creating problems.

Quick question mate…on the diagram is the in4148 anode is also connected to pin #2 of IC2 555 and the cathode is on pin#5 yeah? thanks barbe

absolutely mate, that's corect, without it the IC2 pin3 will not produce a synchronized voltage for the grid integration

im going to try the 6 0 6 aswell..if there is a change..in mosfet temperature…I want it to work mate…appreciated if you could provide everything…:)..:)…I will not stop with this your design…what ever it cos..as I already start on it..so we need to deal with it…

also if you have any latest update on this or anything that maybe I can try..please let me know as I will not retret on this one…really mate…I already blow 3 nos. of transformer 8nos. of mosfet 4nos. 4017ic…how can I stop now..hahahah…

Thanks..Barbe

Yes i can confirmed it is working out of the grid…the only issue was the one mosfet is hotter compare to the other one which just normal temperature…? Thanks Mate

Hi Swag, Thanks for the info… I attached a imaged that maybe a helpful or reason why the mosfet is so hot…could you please if this correct…

s63.photobucket.com/user/barbe10/media/imagejpg1_zps8989a9e2.jpg.html?filters[user]=139832643&filters[recent]=1&sort=1&o=0

Thanks mate….

Barbe, I am afraid that's not correct….the center taps need to be joined together and connected to battery (+) while the upper and lower extreme ends to mosfet drains.

Hi Swag, do you think the polarity of the trnsformer may have an effect on this issue…on 12 0 12? Thanks barbe

Hi Barbe, yes polarity is crucial, I have suggested this in the other article.

First confirm whether your inverter is working correctly without connecting it to the grid.

You can do this by connecting a lamp to it.If the lamp lights up brightly would confirm its working.

Next while integrating it to the grid, connect a lower wattage lamp in series with one of the output terminals of the trafo.

and switch on the inverter.

if the lamp lights up would indicate wrong polarity…reverse the wires and repeat the procedure, this time the lamp should be shutof indicating correct phase polarity.

Barbe as mentioned in the article I'm suggesting all these through my assumptions only, and have never confirmed all these practically…so please be cautious about it.

Good luck mate:)

Hi swag, my 12 0 12 burn…and my my mosfet that is always very hot also burn…the primary 12.0.12. But secondary 220vac is ok??…but i dont know why…? Please if you have any suggestion please…please…

Hi! swag just an update i made to connect to the grid..seems no problem but i think we have a problem with the frequency…i juz dont know where to adjust or what need to be added…possibly from 555 is the issue…

Regarding the mosfet connected to pin2.. Still to hot…i also add another 6amps diode but still hot…i even reduce the zener to 6v. Im wondering why the voltage sometimes is 260vac..specially when i touch the heatsink of mosfet connected to pin2 of 4017…

Please any suggestion mate im out of clue….:(

Thanks..Barbe

ok…mate let me try it..later!!! do you think it is safe know to connect to the grid even I get on my pin type tester a voltage???? on the out put of the transfo?

Thanks Barbe

Hi Swag, 7812…is not working…so i turn back to zener diode its working great.

Another issue why thus mosfet no.1 is much hoter compare to mosfet number 2.? 🙁

OK Barbe no problem, zeners look more appropriate.

No idea mate:(, try checking the gate voltages of the mosfets, are they equal?…or may be the gate zeners may be changed to 6V, could help to keep them cooler

hi Swag, as per above conversation I take your suggestion using 7812 regulator…could you please check if my understanding is correct…or this will help on the issue because..when everything is fine im going to connect this to grid with the input of 18vdc…Thanks

Here is the link below of the diagram,

s63.photobucket.com/user/barbe10/media/Inverterupdate_zps9fa05ffa.jpg.html?filters[user]=139832643&filters[recent]=1&sort=1&o=0

Hi Barbe, the zener and the 1k connections are spot on….

since the zener is connected the 7812 won't be required and can be removed.

You mean no need for the zener diode since the 7812 is already in….i can take it out on pin 16 ic 4017 and 555 both pin 4,8…am i correct please…?

The only concern to me is pin5 of 555 since later im goin to connect it ti 18dc so if i use 7812 it will protected…???

Please for suggestion

Barbe, it's the opposite that I meant…7812 is not required with zener in place.

as mentioned earlier if we use 12V as the supply for the circuit…18V trafo cannot be used…we'll have to go for a 6-0-6 trafo.

Hi swag…i also put now a 12v zener diode supply goin to both 555 ic…but do i need to put 12v zener diode on ic 1 555 pin#5…and i see some improvement the output ac increase to 250vac and when i put the .22uf the voltage increase to 81vac before it juz 67vac…

Thanks..Barbe

Hi Barbe, pin5 may not require a 12V, however with 12V being used for powering the 555s we cannot use a 18v trafo otherwise the grid-tie handshake will not work….

In this case we will have to go for a 6-0-6V trafo and a 12V batt:D

Hi Swag, i attached the link of the caps i put,

s63.photobucket.com/user/barbe10/media/imagejpg1_zpsc9f563a9.jpg.html?filters[user]=139832643&filters[recent]=1&sort=1&o=0

Thanks….

the cap is OK barbe.

Hi swag…some issue…when i put the .22uf/275vac…the output voltage drop to 67vac? Any suggestion please

Hi Barbe,yes it will drop a bit but not to this extent, a 50V drop is acceptable not above this,

try reducing the 022 to 0.1uF and check the results.

hi Swag, 0.1uf has no effect the pin bulb became much brighter…:( from 250vac become 245vac and I heard a like FM generator modulated sound from the transformer…if im not mistaken its kilo hertz that sound not sure…so sure but without caps in the output transformer is silent u can heard very tin modulated sound from transformer…:(

Hi Barbe, a slight noise will be heard due to Magnetostriction effect, but the inclusion will help to reduce bad frequencies from entering the grid and produce cleaner sine waves

if you have an oscilloscope you can watch the effects.

You have any suggestion to eliminate the voltage on the output neutral…??? Im out of clue mate 🙂

Hi Swag, sorry for the comfusion…you mean after the 4148 diode i will 1k in series to the pin16 of 4017ic and zener diode connected to ground and connected aswell to pin16….sorry again i hope my understanding is correct…!! Correct me if im wrong. Thanks barbe

yes that's exactly what needs to be done.

—–>|—————^^^^———–(pin16)————/<———|iii(ground)

1N4148———–1K————–(pin16)———–(zener)—–(ground)

ah…ok im going to do that after work later…how about the zener diode I put in 555ic is it correct after 4148..i connected the 12v zener diode to it…and ground like this..

in —–>|—–(pin 8 of 555)——{<——|iii (ground) is this correct no need another resistor in series after the 4248 diode?

Thanks..:)

Barbe, the zener connection is correct but it will fry without a 1k resistor from the supply.

so please connect a 1k resistor exactly as we did for the 4017 IC.

I did as I notice on 4017 so I copy….:) Thanks MAte

Hi Swag..as you've said..please check the diagram if my understanding on our conversation is correct…:) Thanks Mate

I Attached the link:

s63.photobucket.com/user/barbe10/media/gridtie_zps27cbced1.jpg.html?filters[user]=139832643&filters[recent]=1&sort=1&o=0

Hi Barbe, the junction of pin16 and the 12V zener should be connected to the 1N4148 via a 1k resistor….in your diagram the 1k resistor is missing.

Sure…i will do that and keep you posted on the update…!!! How bout my request man…arc welding machine how can i make 18v secondary and 100amps on a small transformer to weld…i have some burn transfo her at my accomodation im planning to make one to use to handle my solar panel….:)…. Thanks in advance man…in advance if u dont min are you a professor in engeneering or are professional scientist something like that u have a lot of knowledge…!!

Thanks mate, yes I am working on that design and will try to produce it soon in my blog.

18V 100amps through a small trafo could be achieved only with an smps topology, i will discuss it in the proposed article.

I am just an hobbyist like you who has been busy in the field since childhood, nothing much:)

youre a kind of humble mate…youre a scientist to me..you share your knowledge to everyone like a teacher…I hope sometimes we can meet and have a cup of coffee..but im in Dubai..and I think you are in india…:)

for the welding machine im excited mate..:)

thanks so much mate, i too wish we could meet someday.

yes, I'm looking for the welding circuit, and will update it soon as per your request

Sure mate…no prob…i will do that after work…!!! Let you know once its done..

Youve said 6 0 6… I use 12 0 12 for 12volts…but later i will connect it to 18vdc 50watts..solar panel and connect it to the grid…what you think do i need to change it now to 6 0 6 or just keep like that…im using this battery just for testing once its perfect and working i will connect to my solar panel…and install to grid. 🙂 thanks Mate

yep 18v for 12-0-12 trafo would be fine, but make sure the voltage to the ICs are given via zener regulation or 78XX ICs..otherwise they will keep frying up:)

Hi Swag…juz my imagination do you think 2nos. Of 4017ic much better..i dont know???? I just los 3of my 4017..i dont really understand why? Its work perfect…and the next time i check its just not working and 4017 is gone…:(

Hi Barbe, connect the supply to pin16 of iC4017 through a 1k resistor and connect a 12V zener across pin16 and ground, this will prevent the IC from blowing off due to high voltage.

you can do the dame for the 555 supply rails also.

Hi swag…sorry pin# 2 and my 4017 got damged…i juz replace with new one its working again…hope we can make it perfect soon this one mate…..

No problem barbe, take your own time, I appreciate your efforts.

Hi Swag… Again its not working..and mosfet 1 connected to 4017 pin#1 getting to hot…??? I dont know why???just a while ago its working perfect….only few issue is the problem…hassh??.-:(

Hi Swag…as you've said…I put Diode on mosfet…The response was perfect. I attached the photo…

s63.photobucket.com/user/barbe10/media/IMG_20140408_181706_zps5a8fe189.jpg.html

But, Still little have issue here…both output (live and neutral) of the transformer have voltage..when I used pin type tester. I think neutral must be zero and 220vac live. So I have a doubt to connect to main grid yet.

Also, when I used 10watts bulb it glows perfect and even increase the voltage to 248Vac but when I put my soldering iron 35watts the inverter juz stop working output turn to Zero and after I removed its back to normal…I don't know why…?

appreciated much if you give me info on this one…

Thanks In Advance mate…

Barbe

barbe, you can confirm the "phase" terminal of the inverter output by connecting a load across each of the output terminals and external "earthing"….the terminal which switches ON the load could be taken as the phase.

The neon tester could show confusing results due to the high harmonics that could be present i the AC content of the inverter.

In order to negate this you may try adding a 0.22uF/400V capacitor directly across the output terminals of the inverter trafo, this could possibly correct the neon line tester results.

In the image i can see quite a small battery being used, for a 35watt load you would require at least a 10AH fully charged battery….and the trafo voltage must be a little lower than the battery voltage for enforcing proper results.

…for 12V battery, TR2 must be rated 6-0-6V

Ok man Thanks….let you know once im done….

Hi Swag, please check below image if my understanding is correct. Also for both mosfet i need to do it correct. Thanks

s63.photobucket.com/user/barbe10/media/imagejpg1_zps14017bb8.jpg.html?filters[user]=139832643&filters[recent]=1&sort=1&o=0

Yep the polarity and positioning are absolutely correct, but the gate diodes should be 12V zener diodes….not 1N4007

Sure…i will do that…let you know later…about the success if ever but i think it will work…your the brain of all of this…Im just a crazy hobbyst but not like a designer with a gift like you.

Till next time mate….:) im happy as the inverter is making progress..and its working perfect jus need some touch up…and i think it will work smoothly.

Also if you dont mind appreciated if you could design portable arc welding machine with a small transformer only…Thanks in advance for that…

Thank you Barbe, wish you all the best.

If possible i'll surely try to update the arc welding circuit soon in this blog.

I Swagatatam, the normal operation of this inverter should have 220vac output even not connected to the grid or when its not connected to the grid should not have output…l?

Hi Barbe, try putting diodes in series with the drains of the mosfets.

anode to trafo, cathode to drain of the mosfet

use 6 amp diodes.

….also use 12V clamping diodes at the gates of the mosfets.

anode to ground, cathode to gate,

use 1N4007

have some issue again when I connec to the grid the inverter the 44n mosfet get to hot…I didn't put a heat sink yet but…I will try the irf540…I 'll keep you posted..what ever I find out. Thanks

Hi Swagatam, This is good news..it works…perfect. 🙂

s63.photobucket.com/user/barbe10/media/securedownload_zpsd032c117.jpg.html

I Added the picture of the working inverter. Thanks Again

wow! Good job Barbe.

I'll update the image soon in the above article.

thanks very much.

Hi Swag…I just have little issue..sometimes it just have no output 220vac.

When its no output the Z44N mosfet become to hot.. i dont know really is the issue sometimes it works perfect…but not sure if theout put is actually 60hertz but when I connect a bulb on it..it glows and the voltage from the inverter increase which is good sign its working..i keep you posted what is wrong I will figure it out..

Hi swagatam, appreciate if you could provide me the value of the two mosfet as per 12 0 12 10amps, and c3 value. Thanks for your help

Hi Barbe,

you can use IRF540

Thanks

The previous design was busted is not actually work at all…the mosfet got burn though i follow all what in the diagram its become to hot…i dont even have a chance to check the issue but no output of 220vac….i will try this one if will work…i found some new diagram simple and no need transformer…using triacs..i will check that one aswell

Hi Swagatam…is this the same with the previous circuit…this one look simplier…is this operational? Thanks

Hi Barbe, yes it is simpler since it uses the IC 555 configured to generate sine wave equivalent to grid specifications in a Pulse position modulation mode instead of pulse width modulation.

Both are at par but PPM requires a single 555 IC instead of two as in PWM mode.

It looks a viable design to me.

Hi Swagatam Majumdar

transformer ferrit core TR2 change to EI transformer?

thank

yes.

Hi sir

transformer TR2 (ferrit trans)change to EI trans

Hi Khang,

the shown transformers are iron core type, so you can use ordinary step-up trafos for them

Hi Swagatam,

can i use 556 insted of 555?

what is the voltage of the 100uF caps?

how many mosfets if i use IRFZ44n for 1000W?

can u give diagram on how to parallel the Mosfets?

Thanks,

Hi Oiver,

yes 556 can be used here.

100uF voltage rating should be twice that of TR1 output voltage.

you should first try with single mosfets, if it works only then go for more mosfets…

Hi Swagatam,

what about the frequency? is it automatic sync to 50Hz-60Hz?

Thanks,

Hi Oliver,

yes, frequency is also synced with the grid frequency

Hi Swagatam,

can you explain how to get auto frequency from grid base on curcuit diagram.

I am afraid it's not been tested yet completely, Mr. Selim has tried it though but hasn't confirmed the results. I have updated the finalized design…..

Mr. Swagatam, this circuit in August had not yet been tested Do you know if maybe this time someone has tried it and if you have made changes?

Mr. Cabrera, the 1mA symbol is nothing but an arrow mark, ignore it.

C3 = 1uF or any other lower value will also do, it can be a non-polar type for better functionality.

Mr. Swagatam excuceme if I cause trouble, but as I am interested in that I want to loop as shown in the schematic, for this reason I want to know: in the part that is marked (1 mA) between the emitter of T1 and R6 which device is this and the other clarification is what is the value of C3 and whether polarized or not.

Mr. Swagatam excuceme if I cause trouble, but as I am interested in that I want to loop as shown in the schematic, for this reason I want to know: in the part that is marked (1 mA) between the emitter of T1 and R6 which device is this and the other clarification is what is the value of C3 and whether polarized or not.

Mr.Cabrera, you can use any desired transformer as per the load requirements for this design….no adjustments are required here because everything is auto-adjusted as per the data received from the mains AC into the inverters processing circuits.

Mr. Swagatam need some answers on this circuit. I want to know if the power transformer should I do with some specifications or do I just have to output voltage without any variation, I mean, in the normal inverters always the coils are made to a higher voltage and is adjusted with a potentiometer, but no potentiometer here so I want to know what this voltage is synchronized with the network as I do the coil voltage.

Sorry i did not understand your question.

Mr. Swagatam me interested in this circuit for energy saving but I have some questions. As coupling that this investor has the same voltage that has the mains and what is the voltage at which the transformer should I do that attaches to the network if it is 220 volts AC.

as per load and battery

hey hi, suggest me tested inverter circuit upto 500-900W

but my input is BATTERY then what should be the specification 12v 7.5A or 12v 50A and specification of transformer

Hi, battery should be at least 200 AH for supporting 500/900 watts

then, suggest me any other circuit which can give o/p around 500W (modified sine wave) using 12v 50Ah battery.

12V/50AH will not be able to sustain 500 watts.

Hi Roger,

No, it's not a tested design.