In this post we try to investigate how to design a SG3525 full bridge inverter circuit by applying an external bootstrap circuit in the design. The idea was requested by Mr. Mr. Abdul, and many other avid readers of this website.

Why Full-Bridge Inverter Circuit is not Easy

Whenever we think of a full bridge or an H-bridge inverter circuit, we are able to identify circuits having specialized driver ICs which makes us wonder, isn’t it really possible to design a full bridge inverter using ordinary components?

Although this may look daunting, a little understanding of the concept helps us realize that after all the process may not be that complex.

The crucial hurdle in a full bridge or a H-bridge design is the incorporation of 4 N-channel mosfet full bridge topology, which in turn demands the incorporation of a bootstrap mechanism for the high side mosfets.

What's Bootstrapping

So what’s exactly a Bootstrapping Network and how does this become so crucial while developing a Full bridge inverter circuit?

When identical devices or 4 n-channel mosfets are used in a full bridge network, bootstrapping becomes imperative.

It's because initially the load at the source of the high side mosfet presents a high impedance, resulting in a mounting voltage at the source of the mosfet. This rising potential could be as high as the drain voltage of the high side mosfet.

So basically, unless the gate/source potential of this mosfet is able to exceed the maximum value of this rising source potential by at least 12V, the mosfet won't conduct efficiently. (If you are having difficulty understanding please let me know through comments.)

In one of my earlier posts I comprehensively explained how emitter follower transistor works, which can be exactly applicable for a mosfet source follower circuit as well.

In this configuration I have explained that the base voltage for the transistor must be always 0.6V higher than the emitter voltage at the collector side of the transistor, in order to enable the transistor to conduct across collector to emitter.

If we interpret the above for a mosfet, we find that the gate voltage of an source follower mosfet must be at least 5V, or ideally 10V higher than the supply voltage connected at the drain side of the device.

If you inspect the high side mosfet in a full bridge network, you will find that the high side mosfets are actually arranged as source followers, and therefore demand a gate triggering voltage that needs to be a minimum 10V over the drain supply volts.

Once this is accomplished we can expect an optimal conduction from the high side mosfets via the low side mosfets to complete the one side cycle of the push pull frequency.

Normally this is implemented using a fast recovery diode in conjunction with a high voltage capacitor.

This crucial parameter wherein a capacitor is used for raising the gate voltage of a high-side mosfet to 10V higher than its drain supply voltage is called bootstrapping, and the circuit for accomplishing this is termed as bootstrapping network.

The low side mosfet do not require this critical configuration simply because the source of the low side mosets are directly grounded. Therefore these are able to operate using the Vcc supply voltage itself and without any enhancements.

How to Make a SG3525 Full Bridge Inverter Circuit

Now since we know how to implement a full bridge network using bootstrapping, let’s try to understand how this could be applied for achieving a full bridge SG3525 inverter circuit, which is by far one of the the most popular and the most sought after ICs for making an inverter.

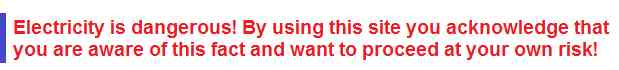

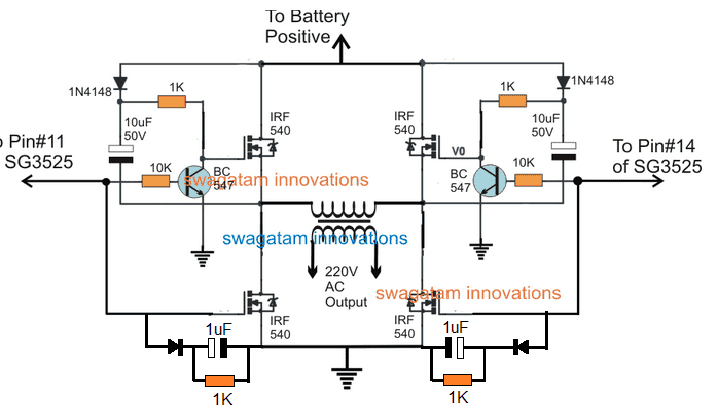

The following design shows the standard module which may be integrated to any ordinary SG3525 inverter across the output pins of the IC for accomplishing a highly efficient SG3525 full bridge or H-bridge inverter circuit.

Circuit Diagram

Referring to the above diagram, we can identify the four mosfets rigged as an H-bridge or a full bridge network, however the additional BC547 transistor and the associated diode capacitor looks a bit unfamiliar.

To be precise the BC547 stage is positioned for enforcing the bootstrapping condition, and this can be understood with the help of the following explanation:

We know that in any H-bridge the mosfets are configured to conduct diagonally for implementing the intended push pull conduction across the transformer or the connected load.

Therefore let’s assume an instance where the pin#14 of the SG3525 is low, which enables the top right, and the low left mosfets to conduct.

This implies that pin#11 of the IC is high during this instance, which keeps the left side BC547 switch ON. In this situation the following things happen withing the left side BC547 stage:

1) The 10uF capacitor charges up via the 1N4148 diode and the low side mosfet connected with its negative terminal.

2) This charge is temporarily stored inside the capacitor and may be assumed to be equal to the supply voltage.

3) Now as soon as the logic across the SG3525 reverts with the subsequent oscillating cycle, the pin#11 goes low, which instantly switches OFF the associated BC547.

4) With BC547 switched OFF, the supply voltage at the cathode of the 1N4148 now reaches the gate of the connected mosfet, however this voltage is now reinforced with the stored voltage inside capacitor which is also almost equal to the supply level.

5) This results in a doubling effect and enables a raised 2X voltage at the gate of the relevant mosfet.

6) This condition instantly hard triggers the mosfet into conduction, which pushes the voltage across the corresponding opposite low side mosfet.

7) During this situation the capacitor is forced to discharge quickly and the mosfet is able to conduct only for so long the stored charge of this capacitor is able to sustain.

Therefore it becomes mandatory to ensure that the value of the capacitor is selected such that the capacitor is able to adequately hold the charge for each ON/OFF period of the push pull oscillations.

Otherwise the mosfet will abandon the conduction prematurely causing a relatively lower RMS output.

Well, the above explanation comprehensively explains how a bootstrapping functions in full bridge inverters and how this crucial feature may be implemented for making an efficient SG3525 full bridge inverter circuit.

Now if you have understood how an ordinary SG3525 could be transformed into a full fledged H-bridge inverter, you might also want to investigate how the same can be implemented for other ordinary options such as in IC 4047, or IC 555 based inverter circuits, …..think about it and let us know!

UPDATE: If you find the above H-bridge design too complex to implement, you may try a much easier alternative

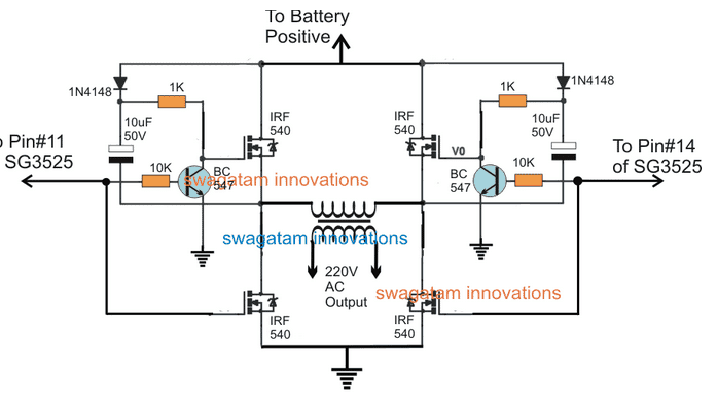

SG3525 Inverter Circuit which can be Configured with the the above Discussed Full Bridge Network

The following image shows an example inverter circuit using the IC SG3525, you can observe that the output mosfet stage is missing in the diagram, and only the output open pinouts can be seen in the form of pin#11 and pin#14 terminations.

The ends of these output pinouts simply needs to be connected across the indicated sections of the above explained full bridge network for effectively converting this simple SG3525 design into a full fledged SG3525 full bridge inverter circuit or an 4 N channel mosfet H-bridge circuit.

An Easier Full Bridge Inverter using P-Channel MOSFET

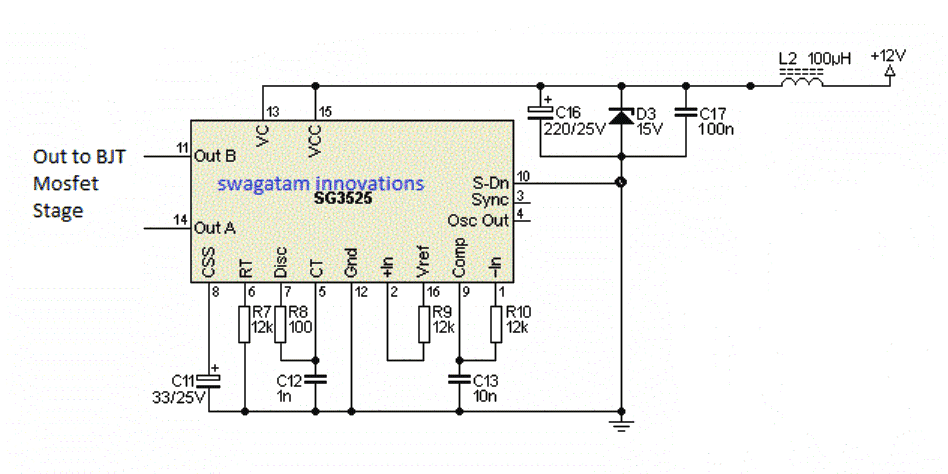

If you think the above SG3525 full bridge inverter circuit using 4 N-channel MOSFETs is too complex for you to handle, then you can rather try the following simpler design.

It replaces the high side N-channel MOSFETs with P-channel MOSFETs, thus eliminating the need of a bootstrapping network.

You can see 3 to 4 P-channel MOSFETs are connected in parallel on the high side, while only single MOSFETs are used on the low side.

This is because P-channel MOSFETs have relatively higher RDSON resistance specifications compared to the N-channel MOSFETs, which have very low RDSON resistance.

To make sure the P-Channel MOSFET's RDSON resistance matches with the N-channel counterpart, more number of P-channel MOSFETs are connected in parallel, which makes sense.

Feedback from Mr. Robin, (who is one of the avid readers of this blog, and a passionate electronic enthusiast):

Hi Swagatum

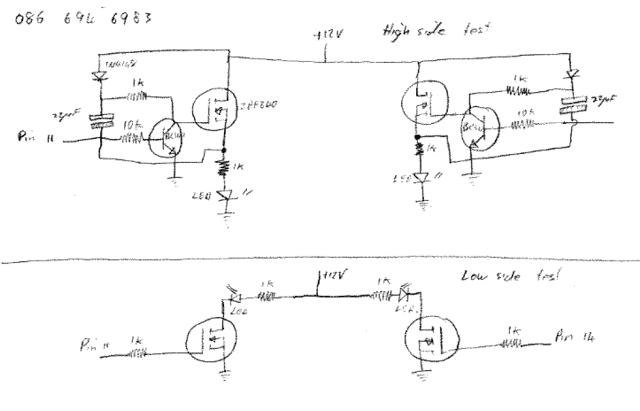

Ok,just to check everything is working I separated the two high side fets from the two low side fets and used the same circuitry as:

(https://www.homemade-circuits.com/2017/03/sg3525-full-bridge-inverter-circuit.html),

connecting the cap negative to the mosfet source then connecting that junction to a 1k resistor and an led to ground on each high side fet.Pin 11 pulsed the one high side fet and pin 14 the other high side fet.

When I switched the SG3525 on both fets lit up momentarily and the oscillated normally thereafter.I think that could be a problem if I connected this situation to the trafo and low side fets?

Then I tested the two low side fets,connecting a 12v supply to a (1k resistor and an led) to the drain of each low side fet and connecting the source's to ground.Pin 11 and 14 was connected to each low side fets gate.

When I switched the SG3525 on the low side fet's would not oscillate until I put a 1k resistor between the pin (11, 14) and the gate.(not sure why that happens).

Circuit diagram attatched below.

My Reply:

Thanks Robin,

I appreciate your efforts, however that doesn't seem to be the best way of checking the IC 's output response...

alternatively you can try a simple method by connecting individual LEDs from pin#11 and pin#14 of the IC to ground with each LED having its own 1K resistor.

This will quickly allow you to understand the IC output response....this could be done either by keeping the full bridge stage isolated from the two IC outputs or without isolating it.

Furthermore you could try attaching a 3V zeners in series between the IC output pins and the respective full bridge inputs...this will ensure that false triggering across the mosfets are avoided as far as possible...

Hope this helps

Best Regards...

Swag

From Robin:

Could you please explain how{ 3V zeners in series between the IC output pins and the respective full bridge inputs...this will ensure that false triggering across the mosfets are avoided as far as possible...

Cheers Robin

Me:

When a zener diode is in series it will pass the full voltage once its specified value is exceeded, therefore a 3V zener diode will not conduct only as long as the 3V mark is not crossed, once this is exceeded, it will allow the entire level of voltage that's been applied across it

So in our case also, since the voltage from the SG 3525 can be assumed to be at the supply level and higher than 3V, nothing would be blocked or restricted and the whole supply level would be able to reach the full bridge stage.

Let me know how it goes with your circuit.

Adding a "Dead Time" to the Low Side Mosfet

Thee following diagram shows how a dead time could be introduced at the low side mosfet such that whenever the BC547 transistor switches causing the upper mosfet to turn ON, the relevant low side mosfet is turned ON after a slight delay (a couple of ms), thus preventing any sort of possible shoot through.

Have Questions? Please Comment below to Solve your Queries! Comments must be Related to the above Topic!!