IC 4018 is a 16-pin CMOS presettable divide-by-N counter, also known as a binary counter. It is commonly used in digital electronics for frequency division and timing applications.

Description

The IC 4018 family includes 5 Johnson-Counter stages, buffered Q outputs from each stage, and counter preset control gating. There are CLOCK, RESET, DATA, PRESET ENABLE, and 5 separate JAM inputs.

Divide by 10, 8, 6, 4, or 2 counter combinations could be achieved by supplying the Q5, Q4, Q3, Q2, Q1 signals back to the DATA input, in that order.

By using a CD4011B to gate the feedback connection to the DATA input, you may build divide-by-9, 7, 5, or 3 counter arrangements. Several CD4018BMS units could be used to create divide-by functions bigger than ten.

During the positive clock-signal transition, the counter advances one count. On the clock line, Schmitt Trigger action allows for infinite clock rise and fall times.

A high RESET signal resets the counter to an all-zero state. A high PRESET-ENABLE signal permits data from the JAM inputs to be used to preset the counter. To ensure the right counting sequence, anti-lock gating is given.

Features:

- Supply voltage range: 3V to 18V

- Low power consumption: typically 10µA at 5V

- Operating temperature range: -55°C to +125°C

- High noise immunity: 0.45Vdd typ.

- Schmitt-trigger input circuitry for noise immunity

- Output capability: standard and high-speed (TC output)

- Pin-compatible with other 4000-series CMOS devices

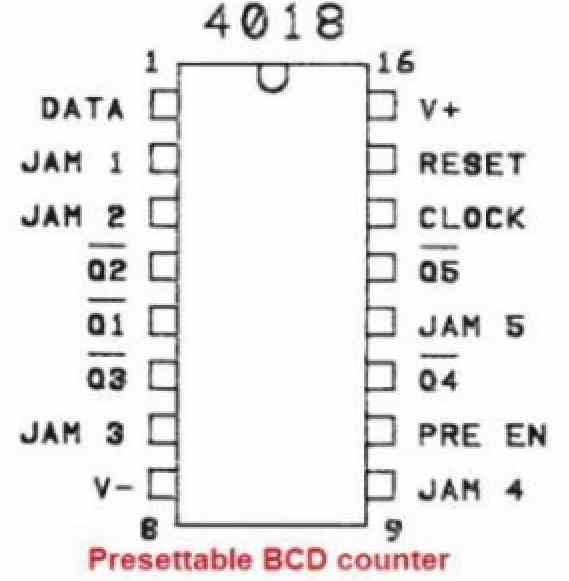

Pinout Description

The pinout details of the IC 4018 can be seen in the following figure:

The IC 4018 is a 4-bit binary counter with a maximum count of 16 (2^4). It can be preset to any value between 0 and 15 using the four preset inputs (Q1-Q4).

The clock input is used to advance the counter by one count on the rising edge of each clock pulse. The clock enable input (Pre EN) and output enable input (OE) are used to enable or disable the clock and output signals, respectively.

The master reset input (MR) is used to clear the counter to zero when pulled low. The carry output (TC) goes high when the counter reaches its maximum count, and can be used to cascade multiple counters for higher counting capability.

Applications:

- Frequency division and timing circuits

- Digital clocks and timers

- Industrial control systems

- Measurement and instrumentation systems

- Counting and sequencing circuits