Here we study a simple IC 555 based monostable circuit whose output monostable time duration starts only after the input trigger is released thus making sure that the trigger ON time duration is added with the monostable's pre-programmed ON time duration. The idea was requested by Mr. John Brogan

Technical Specifications

I would like to know if I could hire you for a very simple project. This is to help me learn circuits.

I am looking for the following type of circuit (see below). Could you let me know what it would cost to design?

There will be 4 pins on the circuit board. 2 pins on the left side of the board, 2 pins on the right.

When someone closes the circuit of the LEFT side of the board, either momentarily, or for however long they keep the circuit closed, the pins on the RIGHT side of the board close *PLUS* 2 minutes after the time the circuit on the LEFT side of the board is opened. (that’s the part I’m stuck on – how to make a circuit stay closed for “n” minutes past the time another circuit is opened.

Please let me know what you would charge to diagram this and list the parts I need to buy to make this.

Thank you!

John Brogan

Colorado

The Design

In other words, the above request demands a monostable whose output on state delay will initiate only once the input trigger is released, meaning suppose the monostable is designed to produce a delay of 2 minutes, and let's assume the input trigger hold time to be x minutes, the total delay at the output pin3 of the IC should be then = 2 minutes + "x" minutes.

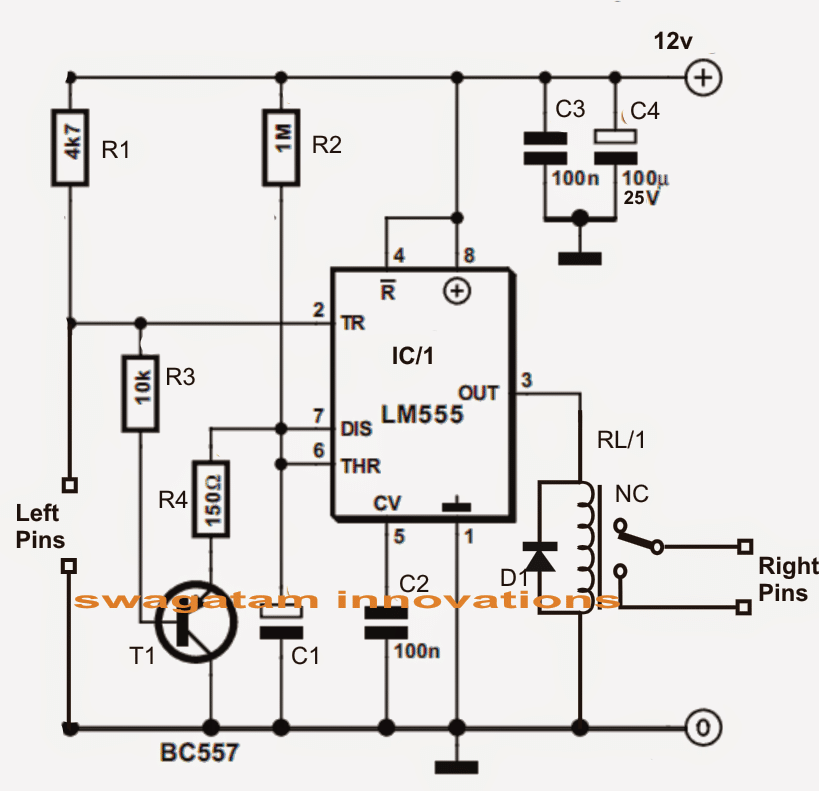

The design may be simply configured by adding a PNP stage to a standard IC 555 monostable circuit.

Referring to the figure below we see a standard IC 555 monostable circuit which produces an output high for a time delay determined by R2 and C1. This initiates each time pin2 is grounded momentarily or may be for some relatively longer period of time.

However normally this would happen as soon as pin2 is grounded without considering the trigger ON duration, and we don't want this situation for the proposed design.

The issue is effectively remedied by the inclusion of the PNP device T1 across the shown position of the circuit.

As suggested in the request when the left pins are closed, T1 is allowed with a negative bias forcing it to conduct.

The above condition allows the output to go high but shorts the timing capacitor C1 via T1 emitter/cpllector so that it is unable to charge until the left pins are opened by the user.

Once the left pins are released, C1 is allowed to charge and initiate the monostable counting operation wherein the relay actuates and closes the right pins for a total duration of the set two minutes plus the duration for which the input was held closed.

Circuit Diagram

IC 555 pinout Specs