Two main types of FETs that presently exist are: JFETs and MOSFETs.

MOSFETs can be further classified into depletion type and enhancement type. Both these types define the fundamental mode of operation of MOSFETs, while the term MOSFET itself is the abbreviation of metal-oxide-semiconductor-field-effect transistor.

Due to the fact that the two types have different working characteristics, we'll be evaluating each of them separately in different articles.

Difference between Enhancement and Depletion MOSFET

Basically, unlike enhancement MOSFETs, depletion MOSFETs are in an on-state even in the presence of a 0 V across the gate-to-source terminals (VGS).

For an enhancement MOSFET, the gate-to-source voltage (VGS) must be above its gate-to-source threshold voltage (VGS(th)) in order to make it conduct.

However, for an N-channel depletion MOSFET, its VGS(th) value is above 0 V. This means that even if VGS = 0 V, a depletion MOSFET is able to conduct current. To turn it off, the VGS of a depletion MOSFET needs to be reduced below the VGS(th) (negative).

In this present article we'll discuss the depletion type MOSFET, which are said to have characteristics matching that of a JFET. The similarity is between cut-off and saturation near IDSS.

Basic Construction

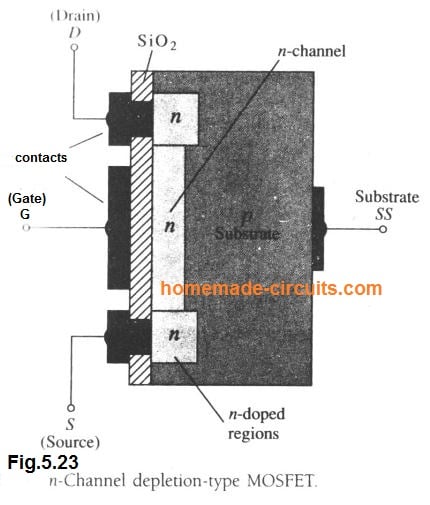

Fig.5.23 shows the basic internal structure of a n-channel depletion-type MOSFET.

We can find a block of p-type material created using a silicon base. This block is called the substrate.

The substrate is the base or the foundation over which a MOSFET is constructed. For some MOSFETs it is internally linked with the "source" terminal. Also, many devices offer an extra output in the form of SS, featuring a 4-terminal MOSFET, as revealed in Fig.5.23

The drain and the source terminals are connected through conductive contacts to n-doped locations, and attached through an n-channel, as indicated in the same figure.

The gate is also connected to a metallic layer, although it is insulated from the n-channel through a fine layer of silicon dioxide (SiO2).

SiO2 possesses a unique form of insulation property called dielectric which creates an opposing electric field within itself in response to an externally applied electric field.

Being an insulating layer, the material SiO2 offers us the following important information:

A complete isolation is developed between the gate terminal and the mosfet channel with this material.

Moreover, it is because of SiO2, the gate of the mosfet is able to feature an extremely high degree of input impedance.

Due to this vital high input impedance property, the gate current IG is virtually zero amps for any dc-biased MOSFET configuration.

Basic Operation and Characteristics

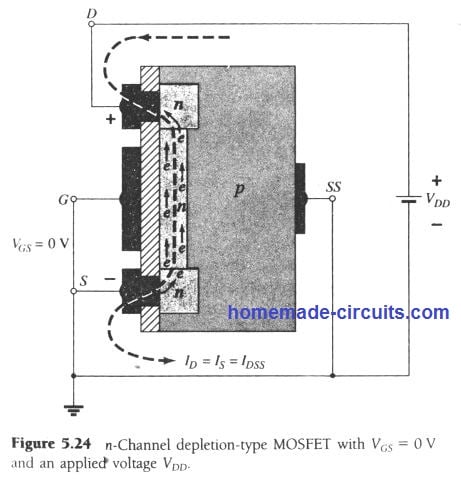

AS can be seen in Fig.5.24, the gate to source voltage has been configured at zero volts by connecting the two terminals together, while a voltage VDS is applied across the drain and source terminals.

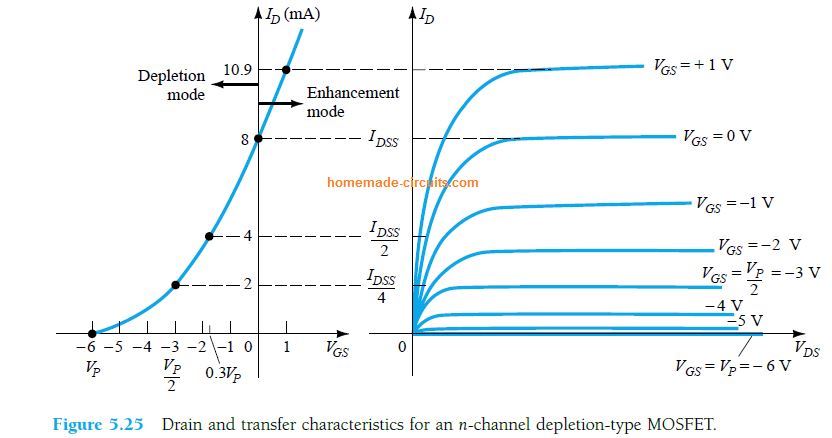

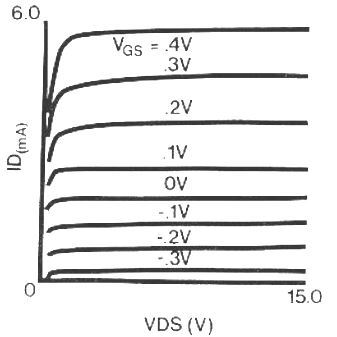

With the above setting, the drain side establishes a positive potential by the n-channel free electrons, along with an equivalent current through the JFET channel. Also, the resulting current VGS = 0V is still being identified as IDSS, as given in Fig. 5.25

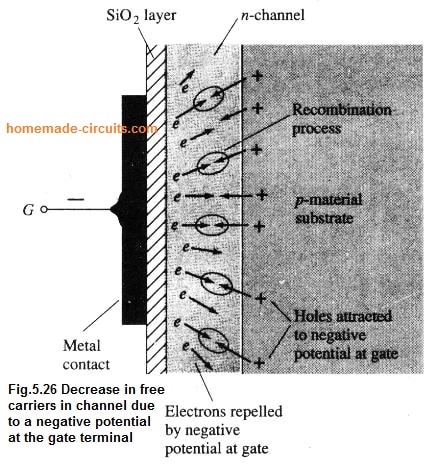

We can see that in Fig.5.26 the gate source voltage VGS is given a negative potential in the form of -1V.

This negative potential tries to force electrons toward the p-channel substrate (since charges repel), and pull holes from the p-channel substrate (since opposite charges attract).

Depending on how large this negative bias VGS is, a recombination of holes and electrons takes place which results in the reduction of free electrons in the n-channel available for the conduction. Higher levels of negative bias results in higher rate of recombination.

The drain current consequently is reduced as the above negative bias condition is increased, which is proven in Fig.5.25 for VGS levels of VGS = -1, -2 and so forth, until the pinch-off mark of -6V.

The drain current as a result along with the transfer curve plot proceeds just like that of a JFET.

Now, for the positive VGS values, the gate positive will attract excess electrons (free carriers) from the p-type substrate, on account of the reverse leakage current. This will establish fresh carriers by the way of resultant collisions across the accelerating particles.

As the gate-to-source voltage tends to rise at the positive rate, the drain current shows a rapid increase, as proven in the Fig.5.25 for the same reasons as discussed above.

The gap developed between the curves of VGS = 0V and VGS = +1 distinctly shows the amount by which the current increased due to the 1 - V variation of the VGS

Due to the fast rise of the drain current we must be careful about the maximum current rating, otherwise it could cross the positive gate voltage limit.

For example, for the device type depicted in the Fig.5.25, applying a VGS = +4V would cause the drain current to rise at 22.2 mA, which may be crossing the maximum breakdown limit (current) of the device.

The above condition shows that the use of a positive gate-to-source voltage generates an enhanced effect on the quantity of the free carriers in the channel, as opposed to when VGS = 0V.

This is why the positive gate voltage region on the drain or transfer characteristics is generally known as enhancement region. This region lies between the cut-off and the saturation level of IDSS or the depletion region.

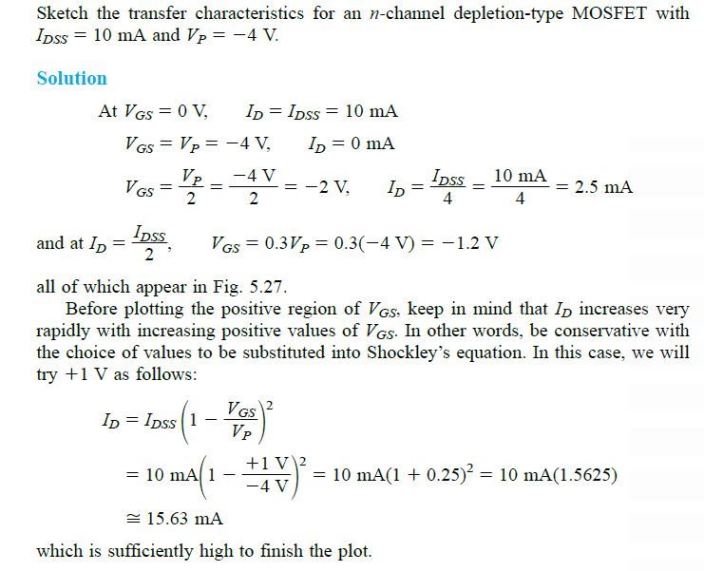

Solving an Example Problem

Advantages and Applications

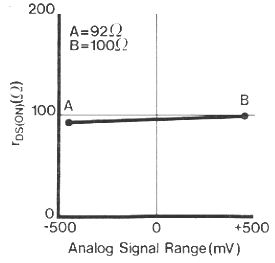

In contrast to enhancement-mode MOSFETs, where we find the drain current dropping to zero in response to a zero gate-to-source voltage, the modern depletion-mode FET features noticeable current with zero gate voltage. To be precise, the drain-to-source resistance is usually 100 Ohms in zero voltage.

As indicated in the above graph, the ON-resistance rds(on) vs analogue signal range looks like a practically flat response. This characteristic, in conjunction with the low-capacitance levels of the these advanced depletion type device, allow them to be specifically ideal as analogue switches for audio and video switching applications.

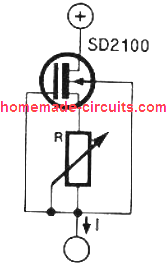

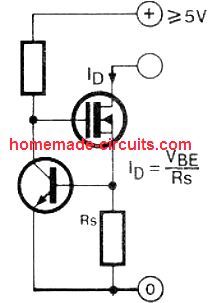

The depletion-mode MOSFET's 'normally-on' attribute enables the device to be perfectly suitable for single FET current regulators.

One such example circuit can be seen in the following figure.

The Rs value could be determined using the formula:

Rs = VGSoff [ 1 - ( ID/IDSS)1/2] / ID

where ID is the amount of regulated current required at the output.

The main advantage of depletion-mode MOSFETs in current-source application is their minimal drain capacitance, that makes them appropriate for biasing applications in low-input leakage, medium-speed (>50 V/us) circuits.

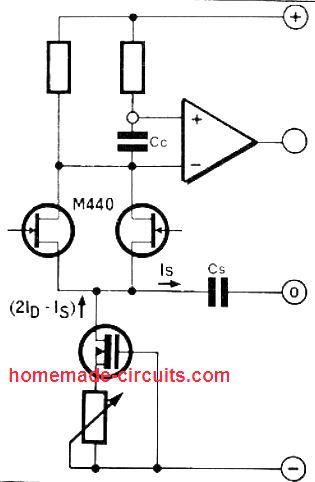

The figure below exhibits a low-input-leakage current differential front-end using a double low-leakage function FET.

Generally speaking, either side of the JFET is going to be biased at ID = 500 uA. Therefore, the current obtainable for charging compensation and stray capacitances becomes restricted to 2ID or, in cases like this, 1.0 mA. The JFET's corresponding features are production-proven and assured on the datasheet.

Cs symbolizes the output capacitance of the input stage 'tail' current source. This capacitance is crucial in non-inverting amplifiers, due to the fact that the input stage experiences significant signal exchanges throughout this network, and the charging currents in Cs could be big. In case normal current sources are employed, this tail capacitance could be accountable for noticeable slew-rate deterioration in non-inverting circuits (compared to inverting applications, where the charging currents in Cs tend to be minimal).

The drop in the slew-rate could be expressed as:

1 / 1+ (Cs/Sc)

So long as Cs is lower than Cc (the compensation capacitor), there may be hardly any variation in the slew rate. Working with the DMOS FET, Cs can be around 2 pF. This strategy produces a huge improvement in the slew-rate. Where current deficits higher than 1 to 5 mA are needed, the device could be biased into the enhancement mode to generate as much as 20 mA for a maximum VGS of +2.5 V, with minimal output capacitance continuing to be a key aspect.

The next application below exhibits a proper enhancement-mode current source circuit.

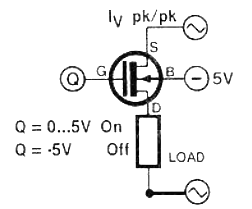

A 'normally-on' analogue switch could be built for requirements where standard condition becomes necessary during a supply voltage failure, for example in automatic ranging of test tools or for ensuring accurate start-up of logic circuits at switch ON.

The reduced negative threshold voltage of the device offers basic drive prerequisites and permits working with minimal voltage.

The circuit below demonstrates the common bias factors for any depletion-mode DMOS analogue switch.

To cause the device to switch off, a negative voltages becomes necessary on the gate. Having said that, the on-resistance could be minimized when the FET is additionally enhanced using a positive gate voltage, enabling it specifically in the enhancement-mode region along with the depletion-mode region.

This response can be witnessed in in the following graph.

The high-frequency gain of the unit, together with its low capacitance values, delivers an increased 'figure of merit'. It is really an crucial element in VHF and UHF amplification, which specifies the gain-bandwidth product (GBW) of the FET, which could be depicted as:

GBW = gfs / 2π(Cin + Cout)

p-Channel Depletion-Type MOSFET

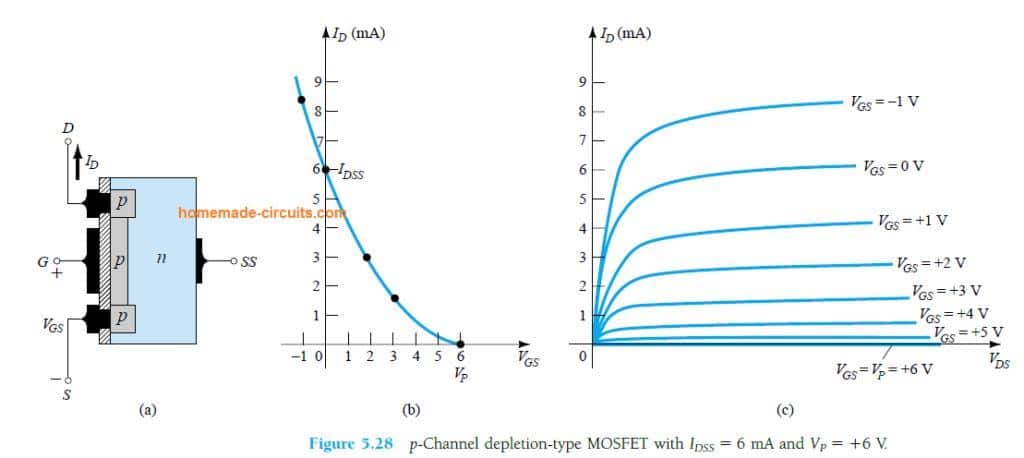

The construction of a p-channel depletion-type MOSFET is a perfect reverse of an n-channel version shown in Fig.5.23. Meaning, the substrate now takes the form of an n-type and the channel becomes a p-type, as can be seen in Fig.5.28a below.

The terminal identification remains unchanged, but the voltage and the current polarities are reversed, as indicated in the same figure. The drain characteristics would be exactly as depicted in Fig.5.25, except VDS sign which will in this case get a negative value.

The drain current ID shows a positive polarity in this case too, that's because we have already reversed its direction. VGS shows an opposite polarity, which is understandable, as indicated in Fig.5.28c.

Because VGS is reversed produces a mirror image for the transfer characteristics as indicated in Fig.5,28b.

Meaning, the drain current increases in the positive VGS region from the cut-off point at VGS = Vp until IDSS, then it continues to rise as the negative value of VGS rises.

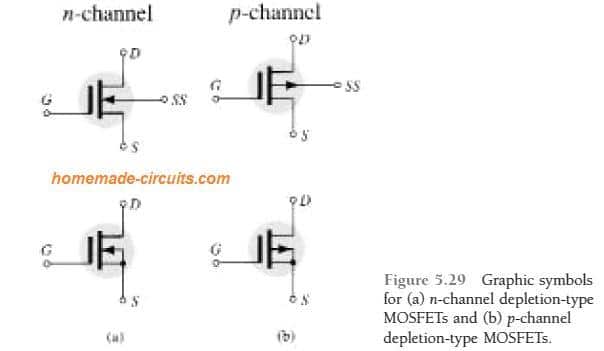

Symbols

The graphical signs for an n- and p-channel depletion-type MOSFET can be witnessed in the above Fig. 5.29.

Observe the way the selected symbols aim to represent the true structure of the device.

The absence of a direct interconnection (because of the gate insulation) between the gate and channel is symbolized by a gap between the gate and the different terminals of the symbol.

The vertical line which represents the channel is attached between the drain and source and is “held” by the substrate.

Two groups of symbols are furnished in the figure above for each type of channel to highlight the fact that in some devices the substrate may be accessible externally while in others this may not be seen.

MOSFET (Enhancement-Type)

Although depletion type and enhancement type MOSFETs look similar with their internal structures and functional mode, their characteristics may be quite different.

The main difference being the drain current which depends on a specific level of gate-to-source voltage for the cut off action.

Precisely, an n-channel enhancement-type MOSFET can work with a positive gate/source voltage, instead of a range of negative potentials which can normally impact a depletion type MOSFET.

Basic Construction

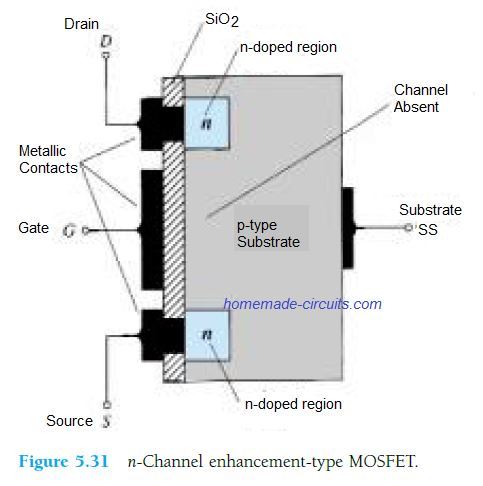

You can visualize the n-channel enhancement-type MOSFET in the following

Fig. 5.31.

A p-type material section is created through a silicon base, and as learned before it is termed as the substrate.

This substrate on some occasions is attached internally with the source pin in a depletion-type MOSFET, while in some instances it is terminated as a fourth lead for enabling an external control of its potential level.

The source and drain terminals are as usual joined using metallic contacts to n-doped regions.

However, it may be important to visualize that in Fig. 5.31 the channel between the two n-doped regions is missing.

This may be considered as the fundamental dissimilarity between a depletion-type and an enhancement-type MOSFET's internal layout, that is an absence of an inherent channel which is supposed to be a part of the device.

The SiO2 layer can be seen still prevalent, which ensures an isolation between the metallic base of the gate terminal and the region between the drain and source. However, here it can be witnessed standing separated from the p-type material section.

From the above discussion we can conclude that a depletion and enhancement MOSFET internal layout may have some similarities, except the missing channel between drain/source for an enhancement type of MOSFET.

Basic Operation and Characteristics

For an enhancement type MOSFET when a 0 V is introduced at its VGS, due to the missing n-channel (which is known to carry a lot of free carriers) causes a current output to be zero, which is quite unlike of a depletion type of MOSFET, having ID = IDSS.

In such a situation due to a missing path across drain/source terminals, large amounts of carriers in the form of electrons are unable to accumulate at drain/source (because of the n-doped regions).

Applying some positive potential at VDS, with VGS set at zero volts and the SS terminal shorted with the source terminal, we actually find a couple of reverse biased p-n junctions between the n-doped regions and the p-substrate to enable any notable conduction across drain to source.

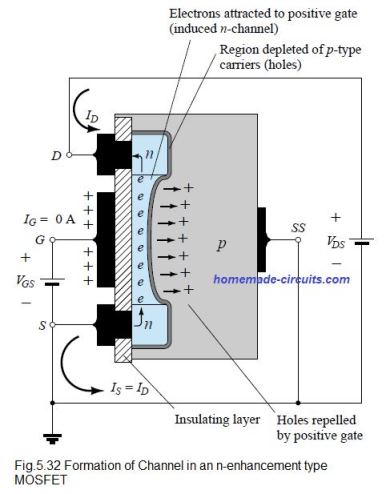

In Fig. 5.32 shows a condition where VDS and VGS are applied with some positive voltage higher than 0 V, allowing the drain and gate to be at a positive potential with respect to the source.

The positive potential at the gate pushes the holes in the p-substrate along the edge of the SiO2 layer departing the location and entering deeper into the regions of the p-substrate, as shown in the above figure. This happens because of the like charges that repel each other.

This results in a depletion region being created close to the SiO2 insulating layer that is void of holes.

Despite of this, the p-substrate electrons which are the minority carriers of the material are pulled towards the positive gate and start gathering in the region close to the surface of the SiO2 layer.

Due to the insulation property of the SiO2 layer negative carriers allow the negative carriers from getting absorbed at the gate terminal.

As we increase the level of VGS, the electron density close to the SiO2 surface also increase, until finally the induced n-type region is able to allow a quantifiable conduction across drain/source.

The VGS magnitude that causes an optimal increase in the drain current is termed as the threshold voltage, signified by the symbol VT. In datasheets you will be able to see this as VGS(Th).

As learned above, due to the absence of a channel at VGS = 0, and "enhanced" with the positive gate-to-source voltage application, this type of MOSFET are known as enhancement-type MOSFETs.

You will find that both depletion- and enhancement-type MOSFETs exhibit enhancement-type regions, but the term enhancement is used for the latter because it specifically works using an enhancement mode of operation.

Now, when VGS is pushed over the threshold value, the concentration of the free carriers will boost in the channel where it's induced. This causes the drain current to increase.

On the other hand, if we keep the VGS constant and increase the VDS (drain-to-source voltage) level, this will ultimately cause the MOSFET to reach its saturation point, as normally would also happen to any JFET or a depletion MOSFET.

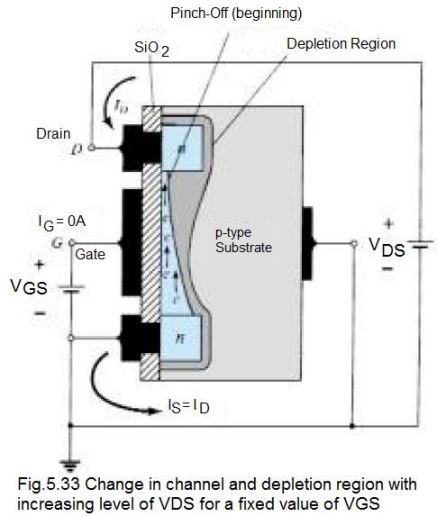

As shown in Fig. 5.33 the drain current ID gets leveled off with the aid of a pinching-off process, indicated by the narrower channel towards the drain end of the induced channel.

By applying applying Kirchhoff’s voltage law to the MOSFET's terminal voltages in Fig. 5.33, we get:

If VGS is kept constant to a specific value, for example 8 V, and VDS is raised from 2 to 5 V, the voltage VDG by Eq. 5.11 could be seen dropping from -6 to -3 V, and the gate potential getting less and less positive with respect to the drain voltage.

This response prohibits the free carriers or electrons from getting pulled towards this region of the induced channel, which in turn results in a drop in the effective width of the channel.

Ultimately, the channel width decreases to the point of pinch-off , reaching a saturation condition similar to what we already learned in our earlier depletion MOSFET article.

Meaning, increasing the VDS any further with a fixed VGS does not affect the saturation level of ID, until the point where a breakdown situation is reached.

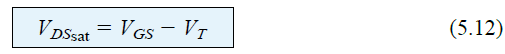

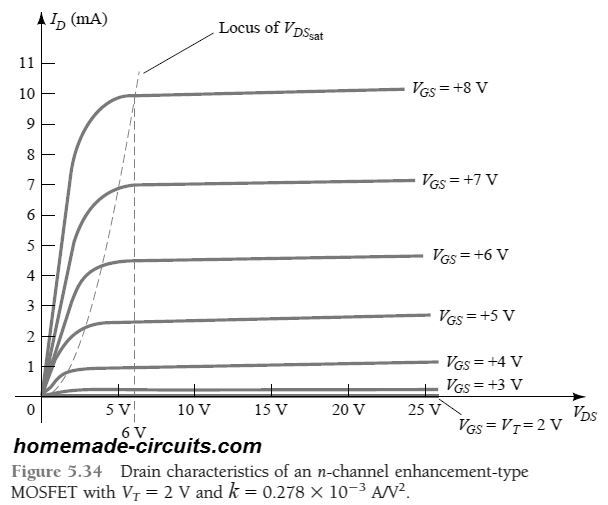

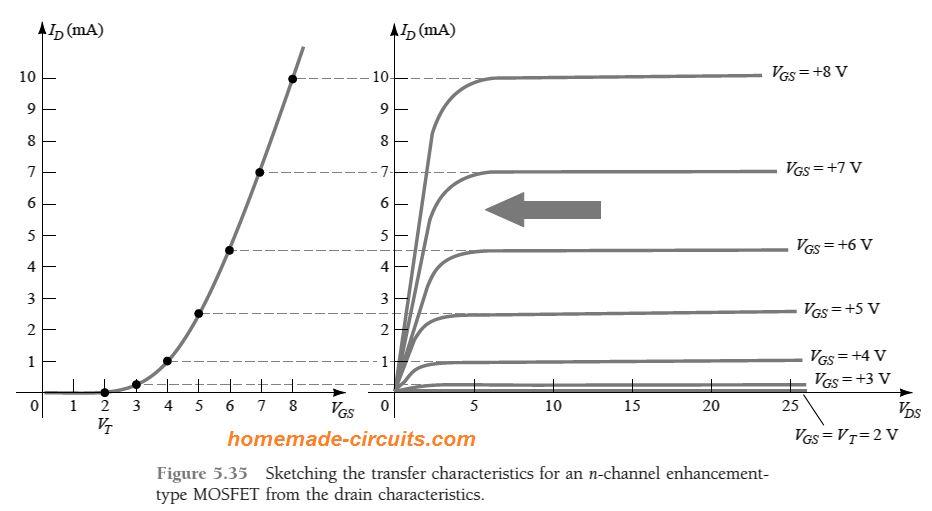

Looking at the Fig 5.34 we can identify that for a MOSFET as in Fig.5.33 having VGS = 8 V, saturation takes place at a VDS level of 6 V. To be precise the VDS saturation level is associated to the applied VGS level by:

No doubt, it thus implies that when the VT value is fixed, increasing the level of VGS will proportionately cause higher levels of saturation for VDS through the locus of saturation levels.

Referring to the characteristics shown in the above figure, the VT level is 2 V, which is evident by the fact that the drain current has fallen to 0 mA.

Therefore typically we can say:

When VGS values are less than the threshold level for enhancement-type MOSFET, its drain current is 0 mA.

We can also clearly see in the above figure that as long as the VGS is raised higher from VT to 8 V, the corresponding saturation level for ID also increases from 0 to 10 mA level.

Moreover we can further notice that the space between the VGS levels increases with an increase in the value of VGS, causing an infinitely rising increments in drain current.

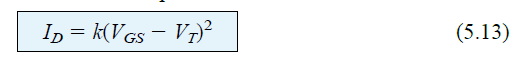

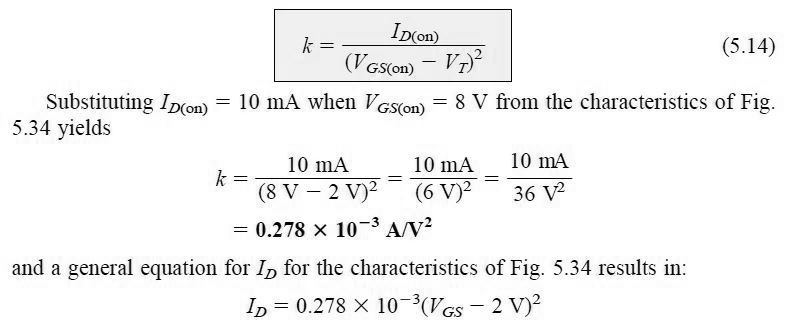

We find the drain current value is related to the gate-to-source voltage for VGS levels that's greater than VT, through the following nonlinear relationship:

The term which is shown squared bracket is the term which is responsible for the nonlinear relatinship between ID and VGS.

The term k is a constant and is a function of the MOSFET layout.

We can find out the value of this constant k through the following equation:

where the ID(on) and VGD(on) each are values specifically depending on the characteristic of the device.

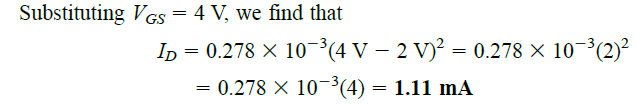

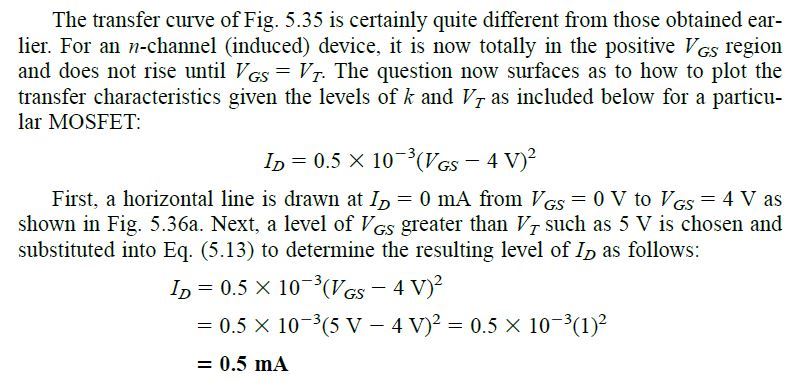

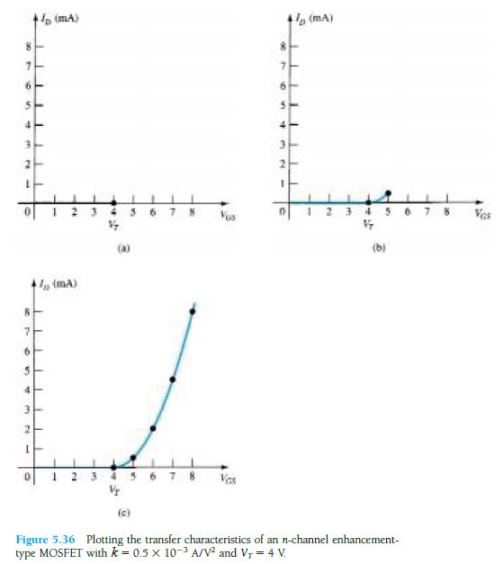

In the next Fig. 5.35 below we find the drain and transfer characteristics are arranged one beside the other to clarify the transfer process across one another.

Basically, it is similar to the process explained previously for JFET and depletion-type MOSFETs.

However, for the present case we have to remember that the drain current is 0 mA for VGS VT.

Here ID may see a noticeable amount of current, which will increase as determined by Eq. 5.13.

Note, while defining the points over the transfer characteristics from the drain characteristics, we only consider the saturation levels. This restricts the region of operation to VDS values higher than the saturation levels as established by Eq. (5.12).

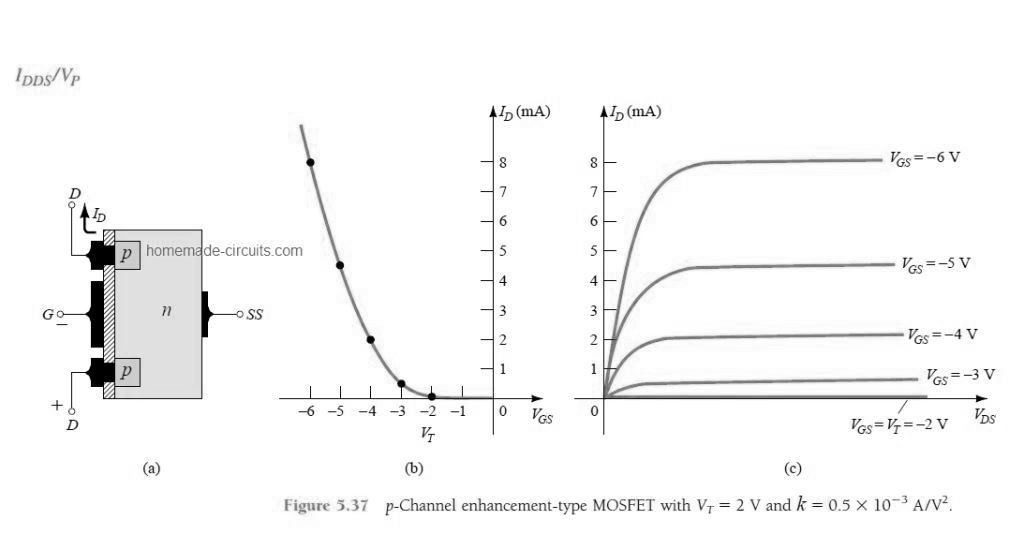

p-Channel Enhancement-Type MOSFETs

The structure of a p-channel enhancement-type MOSFET as shown in Fig. 5.37a is just the opposite of that showing up in Fig. 5.31.

Meaning, now you find that an n-type substrate and p-doped regions beneath the drain and source joints.

The terminals continue to be as established, but each of the current directions and the voltage polarities are reversed.

The drain characteristics can look like as given in Fig. 5.37c, having increasing amounts of current caused by a continuously more negative magnitudes of VGS.

The transfer characteristics would be the mirror impression (around the ID axis) of the transfer curve of Fig. 5.35, having ID increasing with more and more negative values of VGS above VT, as displayed in Fig. 5.37b. Equations (5.11) through (5.14) are similarly appropriate to p-channel devices.

References:

- https://en.wikipedia.org/wiki/MOSFET

- https://hi.wikipedia.org/wiki/%E0%A4%AE%E0%A5%89%E0%A4%B8%E0%A4%AB%E0%A5%87%E0%A4%9F

Hello Swag,

I am not sure this question should be posted here or in the Solid State Relay section, but here goes:

I want to replace a simple 12v NC (normally closed) relay that needs to handle a current (also from a 12v source) of about 200ma. When 12v is also applied to the relay coil, the relay would pull and turn-off the NC circuit. I was thinking that a single MOSFET that is P-channel depletion mode would be able to replace this relay, since it would also act as a NC switch, and allow activation by a positive voltage.

BUT, I can’t find any P-channel depletion mode Mosfets (or don’t know where to look).

This seems like just a simple voltage controlled switch that turns off when 12v is applied.

A Mosfet made sense to me, as it is a voltage controlled switch (with the advantage that no current would be needed to be sourced to activate the switch, as in using a relay or a Bi-polar transistor switch solution.

What I am looking for the simplest/cheapest solution here (in case that is not using a MOSFET)

Can you help?

Thanks,

Walt

Hello Walt,

I think an SPDT relay function can be replicated using two N-channel MOSFETs as presented in the following post:

https://www.homemade-circuits.com/12v-dc-solid-state-relay-ssr-100-amps/

Let me know if you have any further queries or doubts.

The two MOSFET solution you have posted has two different circuits. The first (top) circuit has a description of how it works, but the second (lower and “recommended” one) does not.

Also the lower circuit, seems to have the NO and NC points reversed from the first circuit. (was this intentional?)

Can you please provide a circuit description of how the lower “preferred” circuit works, especially since the NC and NO connections are reversed?

Related to the description,

I also don’t understand the purpose of the optocoupler circuit. (or even what part to get, if it is needed)

Again, what I need is as follows:

In the absence of an input signal, I want to drive a 12v load on a NC output circuit and when a 12v input signal is applied, then the NC circuit should open up to disconnect that load. Can I replace the optocoupler portion of the circuit and just apply 12v directly to the gate of the lower MOSFET in order to disconnect power to my output load?

Thanks for your help,

Walt

The difference between the first and the second circuits is how the gates of the left side MOSFET is connected with the opto-coupler transistor.

In the first design the left MOSFET conducts as the opto-coupler transistor conducts, while in the second design, the left MOSFET conducts when the opto-coupler transistor is turned off and vice versa.

This is why the N/O, N/C are opposite in the two diagrams.

The opto-coupler is there only to provide an isolation between the input signal and the load, if isolation is not required then you can eliminate the opto-coupler and apply the 12V dc signal directly to the gate of the left MOSFET.

For your specific application, you do not need the N/O contact, it can be simply implemented using the following setup:

Take a P-channel MOSFET, connect its source to +12V, connect its gate to ground through a 1k 1/4W resistor.

Connect the load between its drain and the ground line.

Now, when power is switched ON, the MOSFET will conduct and turn ON the load, when a +12V is applied to the gate, the MOSFET will turn OFF and also turn OFF the load….

Can you please suggest a very common and cheap P-channel MOSFET part number(s) for me to look for? Would it be an enhancement-type?

Thanks,

Walt

You can try IRF9540, it is an enhancement-type MOSFET…