This first part of the proposed 4kva synchronized stackable inverter circuit discusses how to implement the crucial automatic synchronization across the 4 inverters with regards to frequency, phase and voltage to keep the inverters running independent of each other yet achieving an output that's on par with each other.

The idea was requested by Mr. David. The following email conversation between him and me details the main specs of the proposed Synchronized 4kva Stackable Inverter Circuit.

Email#1

Hi Swagatam,

Firstly I wanted to say thank you for your contribution to the world at large, the information and most importantly your willingness to share your knowledge to help other people in my opinion is invaluable for many reasons.

I would like to enhance some of the circuits you have shared to suit my own purposes, unfortunately whilst I understand what is going on in the circuits I lack the creativity and knowledge to make the amendments myself.

I can generally follow circuits if they are small and I can see where they join/connect into bigger schematics.

If I may I would like to try to explain what I would like to achieve, though I am under no illusion that you are a very busy person and would not like take up your precious time unnecessarily.

The final goal would be that I would like to build ( assemble the components ) of a multi-source renewable energy micro grid, using Solar PV, Windmills, and bio diesel generators.

The first step is the PV solar inverter enhancements.

I would like to use your 48 volt pure sine wave inverter circuit capable of maintaining a constant 2kW 230V output, it must be capable of delivering at least 3 times this output for a very short duration.

The key modification that I want to achieve it to create a number of these inverters units to work in parallel and connected to an AC bus bar.

I would like each inverter to independently and constantly sample the AC bus bar for frequency, voltage and current (load).

I will call these inverters slave units.

The idea being the invert modules will be “plug and play”.

The inverter once connected to the AC bus bar would constantly sample/measure the frequency on the AC bus bar and use this information to drive the input of a 4047 IC such that its clock output can be advanced or retarded until it exactly clones the frequency on the AC bus bar once the two wave forms are synchronized the inverter will close a contactor or relay which connects the invert output stage to the AC bus bar.

In the event that the frequency on the bar or the voltage moves outside of a pre-determined tolerance the inverter module should open the relay or contactor on the output stage effectively disconnecting the inverter output stage from the AC bar to protect its self.

Additionally once connected to the AC bus bar the slave units would go to sleep or at least the output stage of the inverter would sleep while the load on the bar is less than the sum of all of the slave inverters. Imagine if you will there are 3 slave inverters attached to the AC bus bar, however the load on the bar is only 1.8kW then the other two slaves would go to sleep.

The reciprocal would also be true that if the load on the bar jumped to say 3kW one of the sleeping inverts would instantly wake (already be in sync) to supply the additionally required energy.

I imagine some large capacitors on each of the output stage would supply the energy required whilst the inverter has the very short moment whilst it wakes up.

It would be preferable (only in my opinion) not to directly connect each inverter to each other but rather that they be independently autonomous.

I want to try to avoid micro controllers or the units error or fault checking each other or the units having ‘address’s’ on the system.

In my mind’s eye I imagine that the first connected device on the AC bus bar would be a very stable reference inverter that is constantly connected.

This reference inverter would provide the frequency and voltage that the other slave units would use to generate their own respective outputs.

Unfortunately I can’t get my head around how you could prevent a feedback loop where the slave units would each potentially end up becoming the reference unit.

Beyond the scope of this email I have some small generators I would like to connect to the AC bus bar synchronizing to the reference inverter to supply energy in the event that the load exceeds the DC max output capacity.

The overall premise is that the load presented to the AC bus bar would determine how many inverters and ultimately how many generators would either autonomously connect or disconnect to meet the demand as this would hopefully save energy or at least not waste energy.

The system being completely built of multiple modules would then be expandable/contractible as well as robust/resilient such that if anyone or perhaps two units were to fail the system would continue to function all be it at reduced capacity.

I have attached a block diagram and excluded the battery charging for the time being.

I plan on charging the battery bank from the AC bus and rectifying down to 48V DC this way I can charge from the generators or the renewable energy sources, I do recognize that this is perhaps not as efficient as using DC mppt but I think what I lose in efficiency I gain in flexibility. I live a long way from town or the utility grid.

For reference there would be a minimum constant load on the AC bus bar of 2kW’s though the peak load could rise by as much as 30kW.

My plan is for the 1st 10 to 15kW to be provided by the solar PV panels and two 3kW (peak) windmills the windmills are wild AC rectified to DC and a 1000Ah 48 volt battery bank. (Which I would like to avoid draining/discharging beyond 30% of its capacity to ensure battery life) the remaining infrequent and very intermittent energy demand would be satisfied by my generators.

This infrequent and intermittent load comes from my workshop.

I have been thinking that it may be prudent to build a capacitor bank to handle or pick up the system slack of any inductive load start up currents such as the motor on my air compressor and table saw.

But I am not sure at this time if there is not a better/cheaper way.

Your thoughts and comments would be greatly appreciated and valued I hope you have time to get back to me.

Thank you for your time and attention in advance.

Kind Regards David Sent from my BlackBerry® wireless device

My Reply

Hi David,

I have read your requirement and have hopefully understood it correctly.

Out of the 4 inverters, only one would be having its own frequency generator, while others would be running by extracting the frequency from this main inverter output, and thus all would be in sync with each other and with this master inverter's specs.

I'll try to design it and hope it works as expected and as per your mentioned specs, however the implementation will need to be done by an expert who should be capable of understanding the concept and modify/tweak it to perfection wherever it might be required....otherwise succeeding with this reasonably complex design could become extremely difficult.

I can only present the basic concept and the schematic....rest will need to be done by the engineers from your side.

It might take me some time to complete, this since I already have many pending requests in the Queue...I'll inform you as son as it's posted

Best Regards Swag

Email#2

Hi Swagatam,

Thank you so much for your very prompt response.

That's not quite what I had in mind but certainly represents an alternative.

My thought was that each unit would have two frequency measurement sub circuits one that looks at the frequency on the AC bus bar and this unit is used to create the clock pulse for the inverter sine wave generator.

The other frequency measurement sub circuit would look at the output from the inverter sine wave generator.

There would be a comparison circuit perhaps using an opamp array that would feed back into the inverter sine wave generator clock pulse to advance the clock signal or retard the clock signal until the output from the sine wave generator exactly matched the sine wave on the AC Bar.

Once the frequency of the output stage of the inverter matched the frequency of the AC bus bar there would be an SSR that would close connecting the output stage of the inverter onto the AC bar preferably at the zero cross over point.

This way any one inverter module could fail and the system would carry on functioning. the purpose of the master inverter was that of all the inverter modules it would never go to sleep and would provide the initial AC bar frequency. however if it failed then the other units would not be affected as long as one was 'online'

The slave units should shut down or start up as the load changes.

Your observation was correct I am not an "electronics" man I am a mechanical and electrical engineer 🙂 I work with big plant items like chillers and generators and compressors.

As this project progress's, and starts to become more tangible would you be wiling/open to accept a money gift? I don't have much but I could perhaps gift some money via paypal to help suport your website hosting costs.

Thank you again.

I look forward to hearing from you.

namaste

David

My Reply

Thanks David,

Basically you want the inverters to be in sync with each other in terms of frequency and phase, and also each one having the ability to become the master inverter and takeover the charge, in case the previous one fails due to some reason. Right?

I'll try to fix this with whatever knowledge I have and some common sense and not by employing complex ICs or configurations.

Warmest Regards Swag

Email#3

Hi Swag,

That's it in a nut shell, with taking one additional requirement into consideration.

As the load drops the Inverters go into an eco or standby mode and as the load increases off or increases they wake to meet the demand.

I love the approach you are going with ...

Thank you so much your consideration to me is very greatly appreciated.

Namaste

Kindest Regards

David

The Design

As requested by Mr. David, the proposed 4kva stackable power inverter circuits need to be in the form of 4 separate inverter circuits, which can be stacked up appropriately in sync with each other for supplying the correct amount of self-regulating power to the connected loads, depending on how these loads are switched ON and OFF.

UPDATE:

After some thinking I realized that the design doesn't actually need to be too complicated, rather could be implemented using a simple concept as shown below.

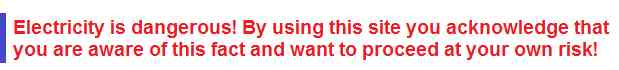

Only the IC 4017 along with its associated diodes, transistors and the transformer will need to be repeated for the required number of inverters.

The oscillator will be a single piece and can be shared with all the inverters by integrating its pin3 with pin14 of the IC 4017.

The feedback circuit must be adjusted precisely for the individual inverters, so that the cut off range is exactly matched for all the inverters.

The following designs and the explanations can be ignored since a much easier version is already updated above

Synchronizing the Inverters

The main challenge here is to enable each of slave inverters to be in sync with the master inverter as long as the master inverter is operational, and in an event (although unlikely) the master inverter fails or stops working, the subsequent inverter takes over the charge and becomes the master inverter itself.

And in case the second inveter also fails, the third inverter takes the command and plays the role of the master inverter.

Actually, synchronizing the inverters is not difficult. We know it can be easily done using ICs like SG3525, TL494 etc. However, the difficult part of the design is to ensure that if the master inverter fails, one of the other inverters is able to quickly become the master.

And this needs to be executed without losing the control over frequency, phase and PWM even for a split second, and with a smooth transition.

I know there can be much better ideas, the most fundamental design for fulfilling the mentioned criteria is shown in the following diagram:

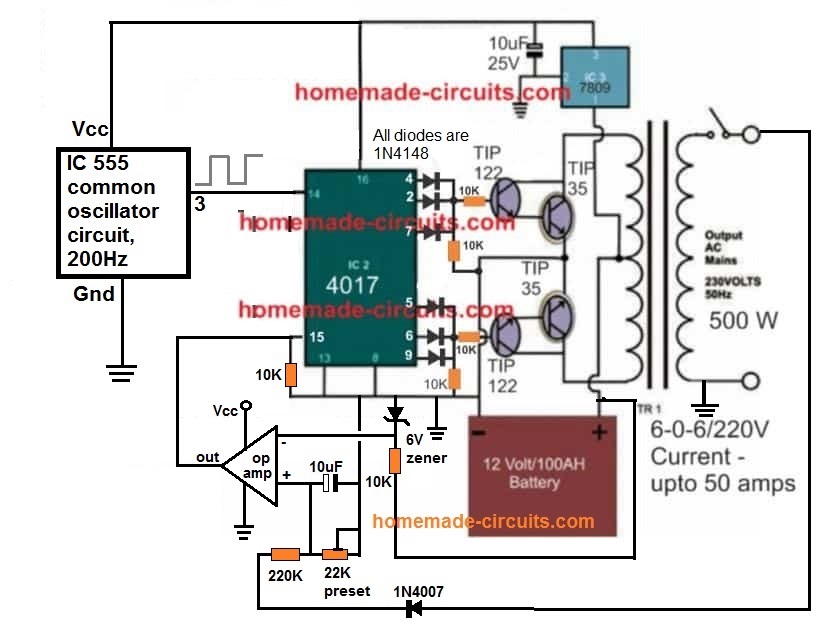

In the figure above we can see a couple of identical stages, where the upper inverter#1 forms the master inverter while the lower inverter#2 the slave.

More stages in the form of inverter#3 and inverter#4 is supposed to be added to the set up in the same identical fashion by integrating these inverters with their indivudual optocoupler stages, but the opamp stage need not be repeated.

The design primarily consists of an IC 555 based oscillator and an IC 4013 flip flop circuit. The IC 555 is rigged to generate clock frequencies at the rate of 100Hz or 120Hz which is fed to the clock input of the IC 4013, which then converts it into the required 50Hz or 60Hz by alternately flipping its outputs with logic high across pin#1 and pin#2.

These alternating outputs are then used for activating the power devices and the transformer for generating the intended 220V or the 120V AC.

Now as discussed earlier the crucial issue here is to synchronize the two inverters so that these are able to run exactly in sync, with regards to frequency, phase and PWM.

Initially all the involved modules (stackable inverter circuits) are separately adjusted with precisely identical components so that their behavior are perfectly on par with each other.

However even with the precisely matched attributes, the inverters cannot be expected to run perfectly in sync unless these are tied up in some unique manner.

This is in fact done by integrating the the "slave" inverters through an opamp/optocoupler stage as indicated in the above design.

Initially, the master inverter#1 is switched ON, which allows the opamp 741 stage to get powered and to initialize the frequency and phase tracking of the output voltage.

Once this is initiated, the subsequent inverters are all switched ON for adding power to the mains line.

As can be seen the opamp output is connected with the timing capacitor of all the slave inverters through an opto coupler which force the slave inverters to follow the frequency and the phase angle of the master inverter.

However the interesting thing here is the latching factor of the opamp with the instantaneous phase and frequency information.

This happens since all the inverters are now delivering and running at the specified frequency and phase from the master inverter, which implies if in case any of the inverters fail including the master inverter, the opamp is able to quickly track and inject the instantaneous frequency/phase info and force the existing inverters to run with this specifications, and the inverter in turn are able to sustain the feedbacks to the opamp stage to make the transitions seamless and self optimizing.

Therefore hopefully the opamp stage takes care of the first challenge of keeping all the proposed stackable inverters perfectly synchronized through a LIVE tracking of the available mains specification.

In the next part of the article we'll learn the synchronized PWM sinewave stage, which is the next crucial feature of the above discussed design.

In the above part of this article I have explained the main section of the 4kva synchronized stackable inverter circuit which explained the synchronization details of the design. In this article we study how to make the design a sinewave equivalent and also ensure correct synchronization of the PWMs across the involved inverters.

Synchronizing Sine Wave PWM across the Inverters

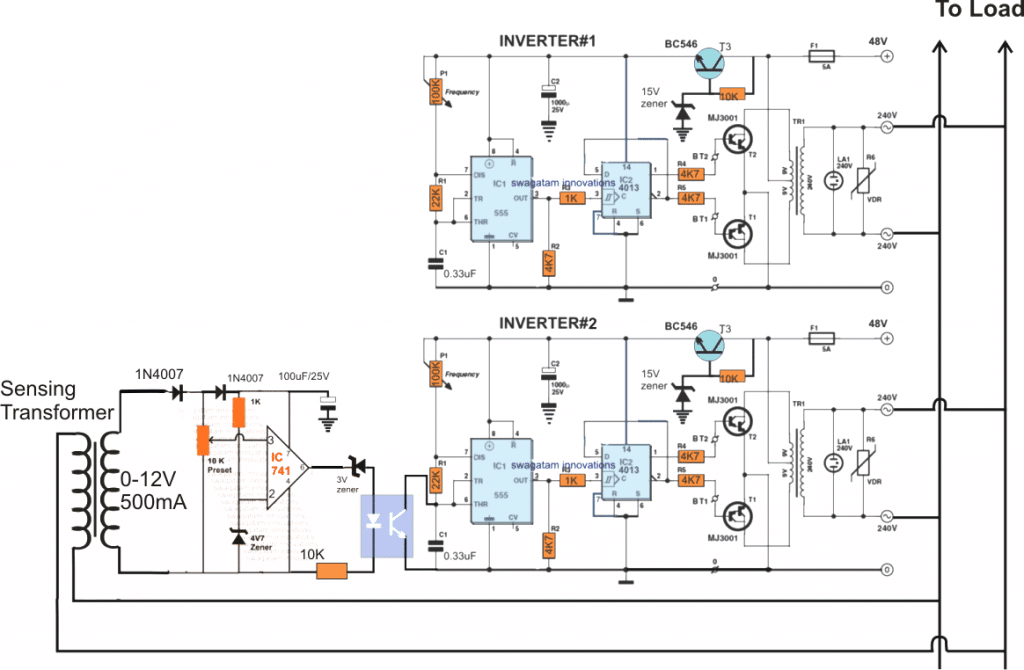

A simple RMS matched PWM equivalent sinewave waveform generator can be made by using an IC 555 and IC 4060, as shown in the following figure.

This design can be then used for enabling the inverters to produce a sinewave equivalent waveform at their outputs, and across the connected mains line.

Each of these PWM processors would be required for each of the stackable inverter modules individually.

UPDATE: It seems a single PWM processor can be used in common for chopping all the transistor bases, provided each MJ3001 base connects with the specific BC547 collector through an individual 1N4148 diode. This simplifies the design to a great extent.

The different stages involved in the above PWM geneartor circuit can be understood with the help of the following point:

Using IC 555 as the PWM Generator

The IC 555 is configured as the basic PWM generator circuit. To be able to generate an adjustable PWM equivalent pulses at the desired RMS the IC requires fast triangle waves at its pin7 and a reference potential at its pin5 which determines the PWM level at its output pin#3

Using IC 4060 as the Triangle Wave Generator

For generating the triangle waves, the IC 555 requires square waves at its pin#2, which is acquired from the IC 4060 oscillator chip.

The IC 4060 determines the frequency of the PWM, or simply the number of "pillars" in each of the AC half cycles.

The IC 4060 is mainly employed for multiplying the sample low frequency content from the inverter output into a relatively high frequency from its pin#7. The sample frequency basically makes sure that the PWM chopping is equal and synchronized for all the invetrer modules. This is main reason why the IC 4060 is included otherwise another IC 555 could have easy done the job, instead.

The reference potential at pin#5 of IC 555 is acquired from an opamp voltage follower shown at extreme left of the circuit.

As the name suggests this opamp delivers exactly the same magnitude of voltage at its pin#6 which appears at its pin#3....however the pin#6 replication of its pin#3 is nicely buffered, and therefore is richer than its pin3 quality, and that's the exact reason of including this stage in the design.

The 10 k preset associated at pin3 of this IC is used for adjusting the RMS level which ultimately fine tunes the the IC 555 output PWMs to the desired RMS level.

This RMS is then applied to the bases of the power devices in order to force them to work at the specified PWM RMS levels, which in turn causes the output AC to acquire a pure sinewave like attribute through a correct RMS level. This may be further enhanced by employing an LC filter across the output winding of the all the transformers.

The next and the final part of this 4kva stackable synchronized inverter circuit details the automatic load correction feature for enabling the inverters to deliver and maintain the correct amount wattage across the output power mains line in accordance with the varying loads switching.

We have so far covered the two main requirements for the proposed synchronized 4kva stackable inverter circuit, which includes synchronization of frequency, phase and PWM across the inverters so that failing of any of the inverters had no effect on the rest in terms of the above parameters.

Automatic Load Correction Stage

In this article we will try to figure out the automatic load correction feature which may enable the switching ON or OFF of the inverters sequentially in response to the varying load conditions across the output mains line.

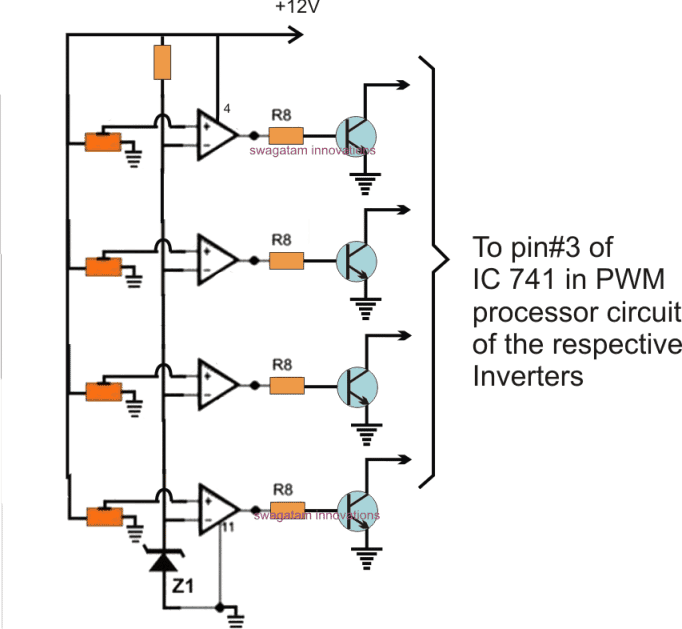

A simple quad comparator using LM324 IC can be used for implementing an automatic sequential load correction as indicated in the following diagram:

In the figure above we can see four opamps from the IC LM324 configured as four separate comparators with their non-inverting inputs rigged with individual presets,while their inverting inputs all referenced with a fixed zener voltage.

The relevant presets are simply adjusted such that the opamps produce high outputs in a sequential a soon as the mains voltage goes above the intended threshold..... and vice versa.

When this happens the relevant transistors switch in accordance with the opamp activation.

The collectors of the respective BJTs are connected with the pin#3 of the voltage follower opamp IC 741 which is employed in the PWM controller stage, and this forces the opamp output to go low or zero, which in turn causes a zero voltage to appear at pin#5 of the PWM IC 555 (as discussed in Part 2).

With pin#5 of the IC 555 is applied with this zero logic, forces the PWMs to become narrowest or at the minimum value, which causes the output of that particular inverter to almost shut down.

The above actions make an attempt to stabilize the output to an earlier normal condition which again forces the PWM to get wider and this tug-of-war or a constant switching of the opamps cintinues consistently keeping the output as stable as possible, in response to the variations of the attached loads.

With this automatic load correction implemented within the proposed 4kva stackable inverter circuit almost makes the design complete with all the features requested by the user in Part 1 of the article.

do you have gerber files and bill of materials list for this stackable inverter?

Sorry, I do not have the BOM and the gerber files for this project. Actually, the above concept is based on my assumptions only, and it first needs to be checked and confirmed on a small scale model, over a general purpose PCB, if it works correctly only then the final PCBs should be designed and built.

can this inverter use 48v so between 38-56v dc? or is it 12v only?

It can handle 48V or higher if the MOSFET and transformer are accordingly rated….

First of all great article. Secondly after reading this and your grid tied inverter article, I had an idea. A grid tied inverter where the mains acts as a backup supply. I’m imagining a scenario where both mains and solar are not 100% guaranteed, but it’s less likely that both be out at the same time. So when grid is available the inverter is aligned with the grid, but if the grid drops out the inverter can continue to supply. However if the grid returns the phase is slowly aligned and finally joined when the alignment finishes.

Your idea makes sense, thanks for the valuable feedback…

After quite some googling I think a static transfer switch could work for the above. Have you got any reference material for such a circuit?

Sorry, I have not investigated the concept so far….and don’t have any reference article on that at this moment…

Hello Swagatam, I found your article pretty interesting. Did you ever tried to connect two inverter in serie to acheive split phase 120/240 ? I have two cotek 1500 sine 48Vdc and these dont come with thefamous syn option. Since the serie connections dont necessarely require current sharing like paralle stack require i think there is no current sensing feedback to be managed betwen both right? can i just use your exemple above with the PWM and 60Hz clock from the master that replace the one of the one from the slave and drive both with the same clock/phase circuit?

Thanks!

Hello Stephane, your concept sounds interesting, but since I have never tried connecting inverter outputs in series, I am having difficulty in simulating the waveform of the series connection output.

Nonetheless you can apply the PWM sync control explained in the above article for keeping all the phases synchronized, there’s another related article from the Grid Tie inverter which could be also tried

Hello Sir.. Thank you for all that you do here. I have read this stackable inverter article many times but am having a difficulty trying to put the complete schematic together. Can you please include the complete schematic of the stackable sinewave inverter as requested by Mr. Dave at the end of the article? It will help me understand it very well as I study your post again.

Thank you for your time sir.

Hello Amos, the diagram being too big can be difficult to shown in one piece, instead you can check out the new updated diagram which looks much easier than the older ones.

Hi Swagatam;

This synchronized stackable inverter is just what i am in need of, just have a few questions if I may on a couple sections I cant seem to piece together.

Your first example with the 555 and 4013 seems fairly strait up except is the sensing transformer required in each slave inverter ?

In the second example circuit, more preferred, you show an opto coupler with reference to “from inverter opamp output ” where is this connected to ?

Then the Automatic Load Correction Stage ,

any recommendations on component values?

Where exactly the outputs suppose to connect at the inverters? says pin #3 of ic 741 but pin 3 is connected to the rms preset …. does this tie in after the preset pot to pin 3 of 741 to tie it to ground to shut down the 555 at pin 5 ?

Thanks

Dave

also what do i need to change to make this 60 hz

C1 can be tweaked accordingly to get 60 Hz

Ah thanks got it now. So at pin 3 of the 741, the rms set all stays, just add lm324 output directly to it ? R8 still needed ?

Oh and it looks like on the inverters 555 output has both 547’s switching at the same time how would that connect to transformer usually it is a flip flop.

Thanks again.

Dave

Yeah that’s right, just make sure to add a 1n4148 diode with each opamp output so that they don’t sink the pin#3 voltage while they are “low”.

The output from the 4013 will switch the transistors alternately ON and OFf, so the PWM BC547 conduction is not going to affect the transistor which is OFf, because the BC547 collectors can only affect the transistor which is ON.

Let me know if you more doubts.

…R8s can be replaced with 1N4148s…….anode towards opamp output

Thanks again, so if I understand this right, need to combine the 2 different inverters by adding the 4013 section behind the 555 in the one with the 4060 instead of the 2 bc547 ? And on the 555 / 4013 inverter what are the BT1 and BT2 between the 4k7 resistor and mj3001 .

Hopefully last thing, the opto for the 4060 all parallel to the 741 in the current sensing transformer circuit ? And is that also where the load correction section gets its 12v supply from , the sensing transformer ?

Hi Dave, sorry I could not understand the following question:

“…adding the 4013 section behind the 555 in the one with the 4060 instead of the 2 BC547”

Yes the optos are supposed to be in parallel, just make sure each opto has its own separate 10K or 4k7 limiting series resistor.

That’s right, load correction gets its supply from the sensing transformer, after the bridge!

Hi Dave,

Only one transformer is required connected with the common mains outputs from the inverter.

The 4060 input signal is acquired from the top IC 741 output, meaning the inputs of the shown two opto-couplers needs to be attached in parallel with the top IC 741 output.

In the automatic correction circuit, the action should be actually opposite. With pin#5 grounded, the BC547 would conduct less, but we want it to conduct more….so we can eliminate all the transistors from the load correction stage, and connect the relevant opamp outputs directly with pin#3 of the IC 741 voltage follower of the PWM stage. This will ensure the correct shut down operations

you will be quite embarrassed to know that you had actually posted your comment under the following article, and not the above article:

https://www.homemade-circuits.com/2016/03/synchronized-4kva-stackable-inverter_23.html

and what kind of offensive pop-up are you referring to??

The pop-up informs the visitors that this site stores cookies in order to know their preferences and to serve better content to them…..

Looks like just about have this nailed down thank you. Oh does the master inverter use the opto and the load correcting lm324 also or is that one omitted ?

What I am asking with the “…adding the 4013 section behind the 555 in the one with the 4060 instead of the 2 BC547”

Is that there are 2 different inverter schematics in this article, if I follow this correctly I need to use the inverter with the4060 and 555 but after the 555 I need to add the 4013 ic and associated components to the 555 output as shown in the first diagram in order to have everything work with as true as possible sine wave output.

Thanks Dave,

The master inverter does not use an opto near the IC 555 but it uses the PWM integration across the power transistor baeses. It is the master inverter so its frequency and peak voltage governs the other inverters as long as it’s working.

the 4060 section is not an inveter stage, it’s the PWM chopping stage for carving the squares waves into PWM sine wave across the inverter power transistors bases.

Just wanted to remind you that the concept has been assumed by me through mind simulation, I have not yet practically confirmed the design, so please proceed with caution.

Yes I understand this is concept so far, I think I have it sorted out do you have somewhere I can send you a touch schematic to check over to see if I sorted it right ?

Hi sir, sir can you show me how to obtain electricity from steam sir. thx sir

Tun, you can use the principle of steam engine and connect it with an alternator shaft

sir, the link was totally wrong sir.

sorry, here's the correct one:

https://www.homemade-circuits.com/2012/10/1-watt-led-driver-using-joule-thief.html

Hi Sir, i here again to ask if there is a way of charging a capacitor e.g(1000/16v) cap. with 4.50 battery… pls show me if there is. Thank you sir, pls keep the good work.

OK! ,thank u sir

Hi sir, i wanna ask a question sir, anyway it base on rechargeable lamp… let me be straight to the point , one out of two capacitors inside(electrolytic: 100mf/50) get blown out few month ago, but now, i'm trying to replace it with another ca.(100mf/16v) . So will it work smoothly sir.

Tun, the voltage rating of the cap must be ideally twice that of the supply voltage rating….if you have ensured this then it's fine.

By the way it's important to check why and how the previous cap blew

oh no!, this can't be good , anyway thank you sir.

ok here is the youtube link, i watch the video anyway.pls help i'm stuck sir. m.youtube.com/watch?v=VDi_uFSr3w0&itct=CBgQpDAYASITCKa7n-CvqM0CFeIkfgodRfIA6DIHcmVsYXRlZEiv85u6n5Wj3RU%3D&hl=en&gl=NG&client=mv-google

Tun, your circuit may not be working due to one of the following reasons:

1) fault in the connections or the mosfet orientation.

2) transformer is not rated at the specified current…remember trafo is the heart of the design, if it's incorrectly designed then the outcome will be affected.

3) your battery is not fully charged.

check by connecting an ammeter in series with the battery positive…if the current is nil then definitely your circuit connections are not correct, if it's low then either the connections are faulty or the trafo or the battery could be incorrectly rated

hello sir pls i need a circuit of a variable power supply that ranges from 0-70v both AC & DC output, 5amps current. thank you sir

Hello Dairo, AC is not possible with a DC circuit, you will need a vriac for this.

for DC variable control you can try the following design:

https://www.homemade-circuits.com/2012/01/how-to-make-versatile-variable-voltage.html

hello sir please i need a circuit diagram of a variable power supply ranges from 0-70v both in AC and DC 5amps

Swagatam Majumdar, All right? Sorry for my English translated from Portuguese I speak. This project, the scheme only if I use an inverter, I observed that the switching transistors of power are the MJ3001 that are capable of dissipating 150W with 80 volts and 10 amps. what would be the power produced by a single inverter with a pair of MJ3001 as shown in your scheme? Can I put more pairs of MJ3001 to increase to at least 3kw of power output to power single-phase motors 110vac or 220vac for pumping fresh water? I could make this change for my purpose of use? I thank you for your readiness to help others with their intelligence and kindness. Big hug.

Hi Killer, the above concept is posted as an example only, and could be upgraded to any possible limits as per the users demands.

You can easily modify the power devices by adding more numbers in parallel or replace them with mosfets for getting much higher outputs for driving any form of equivalent loads.

you are most welcome!

Sir..

I want to make a circuit in which the gears changed in motorcycle should be shown on a screen..! Same as how the left indicator is turned on it shows that the indicator is been made on on dt screen.

Similarly.. When I change the gears it should also show me.. on which gear im running mymotorcycle.

Sir.. This is very helpful..!!

So plz sir… Can u make this circuit..!! It's urgent .!!

Rayan, I'll try to design the circuits, but it might take some time to finish it, since I have many other pending assignments to complete

sir..

I'm also having another idea…!!

usually brake lights of a motorcycle light up

onli when brakes are applied..!! BT usually the

motorcycle speed is reduced by changing

down the gears.. so can u make a circuit in

such a way that the brake lights light up

depending on the speed reduced in the egine

.. even though the brakes are applied or not..!!

plz sir.. I need ur help..!! I'm sure u can make

a circuit for this one…!!

Hi Rayan,

yes that's possible, but I am not sure whether that will be approved by RTO or not. yes I can make it